Recursos de Economia de Energia

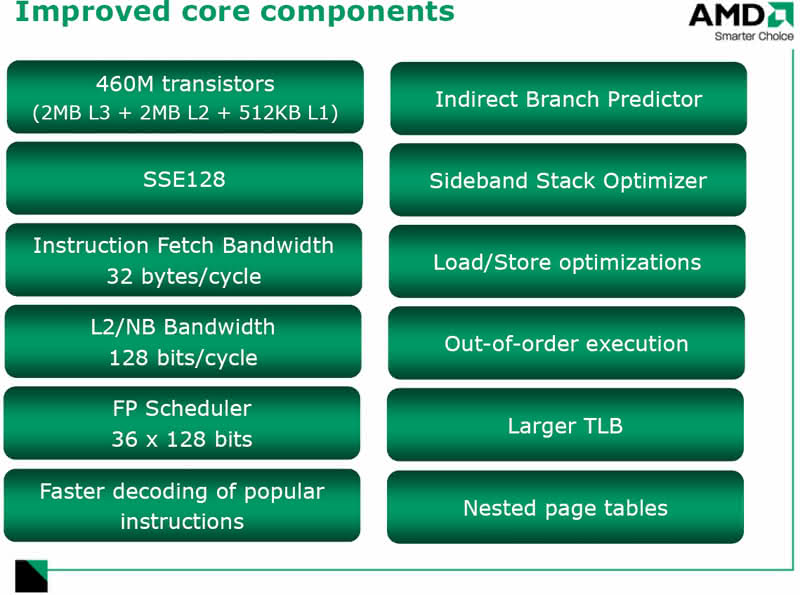

A maioria das novas funcionalidades introduzidas pela a nova arquitetura K10 é destinada à economia de energia – o que faz com que o processador produza menos calor.

Esses recursos são:

- Tecnologia de Núcleo Dinâmico Independente (Independent Dynamic Core Technology), que permite que cada núcleo do processador trabalhe com um clock diferente. A tensão de alimentação dos núcleos, no entanto, é compartilhada e será a tensão exigida pelo o núcleo que estiver trabalhando com o clock mais elevado.

- Tecnologia CoolCore, que permite ao processador desligar automaticamente partes que não estejam sendo usadas. Os processadores baseados na microarquitetura Core têm uma tecnologia similar chamada Chaveamento Elétrico Avançado (“Advanced Power Gating”).

Figura 6: Tecnologia CoolCore.

- Gerenciamento Elétrico Dinâmico Duplo (Dual Dynamic Power Management, DDPM), informalmente conhecida como “split-plane” (“alimentação dividida”), esta tecnologia permite que o processador e o controlador de memória (que está embutido dentro do processador) usem linhas separadas de alimentação – ou seja, tenham tensões de alimentação diferentes. Isto permitirá que o controlador de memória trabalhe com clocks mais elevados – tipicamente 200 MHz acima do clock padrão. Esta tecnologia permite ainda que o processador reduza sua tensão de alimentação e mantenha o controlador de memória trabalhando em seu desempenho máximo, quando o processador entrar em um de seus modos de economia de energia. Quando instalada em placas-mães mais antigas que não tenham alimentação separada para o processador e para o controlador de memória, o processador trabalhará igual aos processadores com arquitetura K8, ou seja, usará apenas uma única tensão para alimentar tanto o processador quanto o controlador de memória.

Figura 7: Gerenciamento elétrico dinâmico duplo (DDPM).

Figura 8: Gerenciamento elétrico dinâmico duplo (DDPM).

- Os processadores para computadores de mesa usarão o barramento HyperTransport 3.0 em vez do barramento HyperTransport 1.x (processadores para servidores usarão o HT3 no futuro). Há dois objetivos aqui. O mais óbvio é uma maior taxa de transferência para acessar periféricos, já que usando o HT3 os processadores baseados na microarquitetura K10 serão capazes de acessar o mundo externo a até 10.400 MB/s (processadores baseados na arquitetura K8 são capazes de efetuar transferências a até 4.000 MB/s) – isto é um importante aumento de 2,6 vezes na largura de banda disponível. Mas a vantagem não tão óbvia é a economia de energia, há que o HT3 permite que o processador mude o clock do barramento HyperTransport e a quantidade de bits que são transferidos por pulso de clock automaticamente. Por exemplo, se o processador sente que a taxa de transferência de 10.400 MB/s é muito alta para o que ele está fazendo no momento, ele pode diminuir o clock do barramento HyperTransport (e a quantidade de bits transmitidos) para um valor mais compatível para o que ele esteja fazendo. Quanto menor o clock e o número de bits transmitidos por pulso de clock, menor é o consumo elétrico. Como o HT3 mantém compatibilidade com o HT1, os processadores baseados na arquitetura K10 podem ser instalados em placas-mães antigas, mas seu barramento HyperTransport trabalhará com um clock menor. Para uma discussão mais detalhada sobre o HyperTransport 3.0 leia nosso tutorial O Barramento HyperTransport usado pelos Processadores da AMD.

Vamos falar agora sobre os processadores que usarão a nova arquitetura K10.

(18).thumb.jpeg.07124b4b6655ce105844b9e834d330f8.jpeg)

Respostas recomendadas

Crie uma conta ou entre para comentar

Você precisa ser um usuário para fazer um comentário

Criar uma conta

Crie uma nova conta em nossa comunidade. É fácil!

Crie uma nova contaEntrar

Já tem uma conta? Faça o login.

Entrar agora