Novas Instruções

O conjunto de instruções AVX2 expande o conjunto de instruções AVX existente para permitir o uso de registradores de 256 bits com operações de números inteiros. No conjunto de instruções AVX, as operações com números inteiros estão limitadas a registradores de 128 bits e registradores de 256 bits são usados apenas em operações de ponto flutuante.

Além disso, o conjunto de instruções AVX2 suporta instruções FMA (Fused Multiply-Add ou Adição e Multiplicação Fundidas) de três operandos (também chamado FMA3), que é capaz de executar operações como a x b +c com uma única instrução. Essas instruções já eram suportadas pelos processadores da AMD baseados na microarquitetura Piledriver. Duas unidades de execução FMA foram adicionadas à microarquitetura, como mostraremos na próxima página.

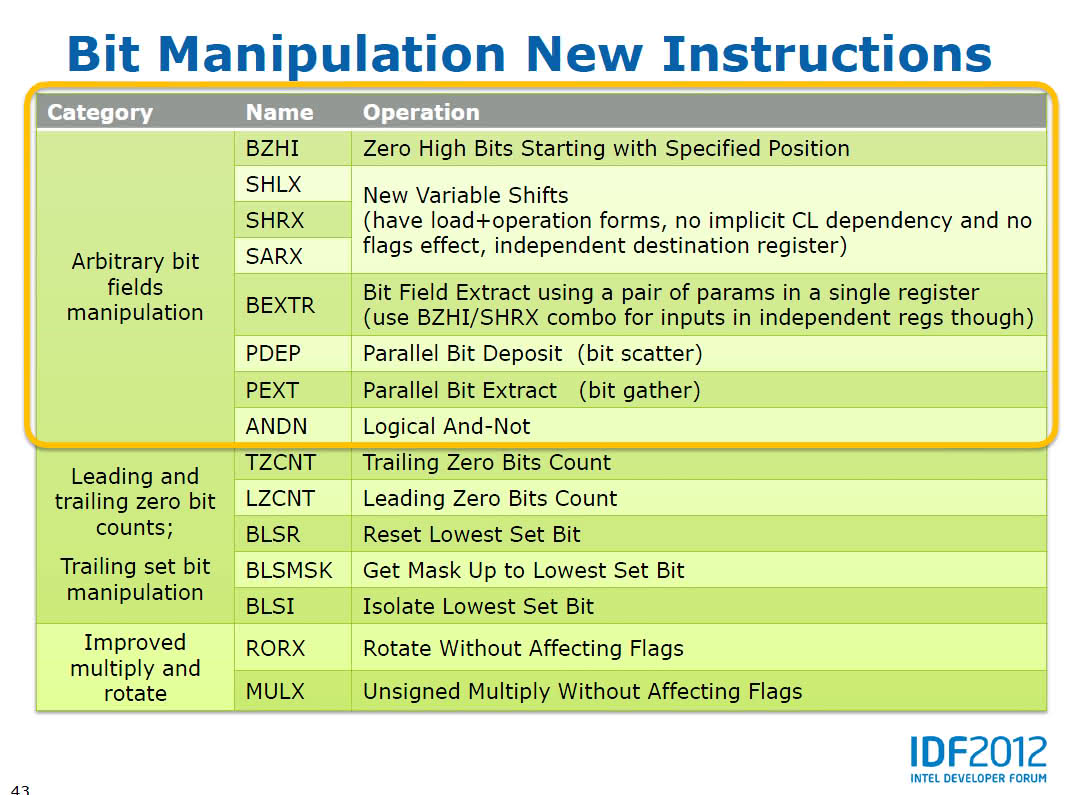

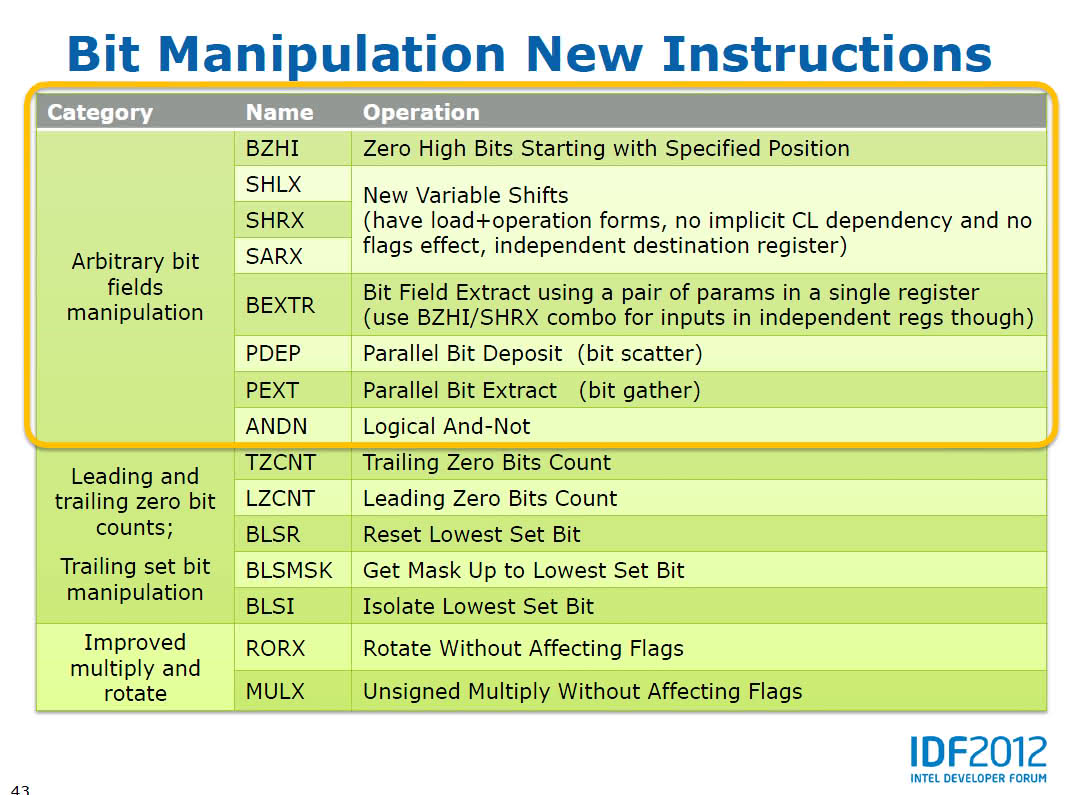

Quinze novas instruções de manipulação de bit (BMI, Bit Manipulation Instructions) foram adicionadas. Essas instruções, que estão listadas na Figura 1, podem ser usadas para criptografia, indexação e conversão de dados.

Figura 1: Novas instruções de manipulação de bit

O terceiro conjunto de instruções adicionado à microarquitetura Haswell é chamado TSX (Transactional Synchronization eXtensions ou Extensões de Sincronização de Transações) e é usado para ajudar na solução de problemas de sincronia de dados quando um mesmo dado pode ser usado por processos diferentes que estão rodando ao mesmo tempo.

Todos os novos conjuntos de instruções estão descritos em detalhes no documento “Intel Architecture Instruction Set Extensions Programming Reference”. (O arquivo baixa sem uma extensão; é um arquivo PDF).

Para usar qualquer um desses conjuntos de instruções, é claro que o programa que você estiver rodando deverá suportá-los.

Respostas recomendadas

Crie uma conta ou entre para comentar

Você precisa ser um usuário para fazer um comentário

Criar uma conta

Crie uma nova conta em nossa comunidade. É fácil!

Crie uma nova contaEntrar

Já tem uma conta? Faça o login.

Entrar agora