Índice

Índice

- Introdução

- RAM Dinâmica vs. RAM Estática

- História do Cache de Memória nos PCs

- O Cache de Memória

- Cache de Memória L2 nos Processadores Multi-Núcleos

- Como o Cache de Memória Funciona

- Organização do Cache de Memória

- Cache Associativo por Grupos de n-vias

- Configuração do Cache de Memória nos Processadores Atuais

Como o Cache de Memória Funciona

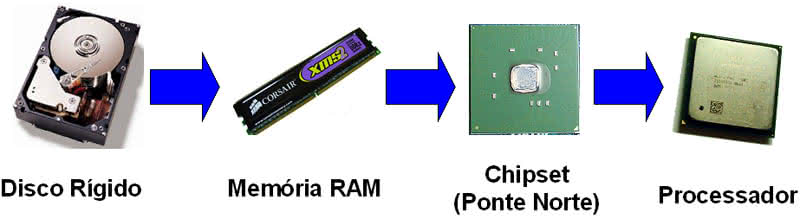

O cache de memória funciona da seguinte forma. A unidade de busca do processador procura pela a próxima instrução a ser executada no cache L1 de instruções. Se ela não estiver lá, o processador procurará por ela no cache L2. Por fim, se a instrução não estiver no cache L2, o processador terá que buscá-la na memória RAM.Chamamos de “acerto” (“hit”) quando o processador carrega uma informação requisitada do cache, e de “erro” (“miss”) quando a informação requisitada pelo processador não está no cache de memória e ele precisa acessar a memória RAM do micro.

Claro que quando você liga o micro os caches estão vazios, assim o processar tem de acessar a memória RAM – este é um erro do cache inevitável. Mas após a primeira instrução ter sido carregada, o show começa.

Quando o processador carrega uma instrução de uma certa posição da memória, um circuito chamado controlador de cache carrega para o cache de memória um pequeno bloco de dados abaixo da posição atual que o processador acabou de carregar. Como os programas normalmente seguem um fluxo sequencial, a próxima posição de memória que o processador precisará provavelmente será a posição de memória imediatamente inferior a qual o processador acabou de carregar. Como o controlador de memória já carregou alguns dados abaixo da primeira posição de memória lida pelo o processador, o próximo dado provavelmente já estará dentro do cache de memória. Portanto o processador não precisará buscar o dado na memória RAM: o dado já foi carregado para o cache de memória embutido no processador e pode ser acessado com o clock interno do processador.

Esta quantidade de dados é chamada linha e é normalmente de 64 bytes (mais sobre esse assunto na próxima página).

Além de carregar esta pequena quantidade de dados, o controlador de memória está sempre tentando adivinhar qual será o próximo dado que o processador precisará. Um circuito chamado pré-busca, por exemplo, carrega mais dados localizados após esses primeiros 64 bytes da RAM dentro do cache de memória. Se o programa continuar carregar instruções e dados de posições de memória sequenciais, as instruções e dados que o processador precisará já estarão localizadas dentro do cache de memória.

Portanto nós podemos resumir como o cache de memória funciona da seguinte forma:

- O processador solicita a instrução/dado armazenado no endereço “a”.

- Como o conteúdo do endereço “a” não está no cache de memória, o processador precisa buscá-lo diretamente da memória RAM.

- O controlador de cache carrega uma linha (tipicamente de 64 bytes) começando do endereço “a” para dentro do cache de memória. Isto é, mais dados do que o processador solicitou, portanto se o processador continuar executado o programa sequencialmente (isto é, solicitando o endereço a+1) a próxima instrução/dado que o processador precisará já estará localizada no cache de memória.

- Um circuito chamado pré-busca carrega mais dados localizados após esta linha, ou seja, carrega o conteúdo do endereço a+64 para dentro do cache. Para dar a você um exemplo real, os processadores Pentium 4 têm um circuito de pré-busca de 256 bytes, o que significa que ele carrega os próximos 256 bytes após a linha recém carregada para dentro do cache.

Se os programas sempre forem executados sequencialmente o processador nunca precisará buscar dados diretamente da memória RAM – exceto para carregar a primeira instrução – já que as instruções e dados solicitados pelo o processador já estariam dentro do cache de memória antes de o processador solicitar por eles.

Porém os programas não são executados dessa forma, de tempos em tempos eles pulam para outra posição de memória. O principal desafio do controlador de cache é tentar adivinhar para quais endereços o processador pulará, carregando o conteúdo desses endereços para o cache de memória antes que o processador os solicite, de modo a evitar que o processador acesse a memória RAM, que é lenta. Esta tarefa é chamada previsão de desvio e todos os processadores modernos têm esse recurso.

Os processadores modernos têm uma taxa de acerto de pelo menos 80%, o que significa que pelo menos em 80% do tempo o processador não acessa a memória RAM diretamente, mas sim o cache de memória.

Respostas recomendadas

Crie uma conta ou entre para comentar

Você precisa ser um usuário para fazer um comentário

Criar uma conta

Crie uma nova conta em nossa comunidade. É fácil!

Crie uma nova contaEntrar

Já tem uma conta? Faça o login.

Entrar agora