Aprimoramentos no Pipeline do Processador

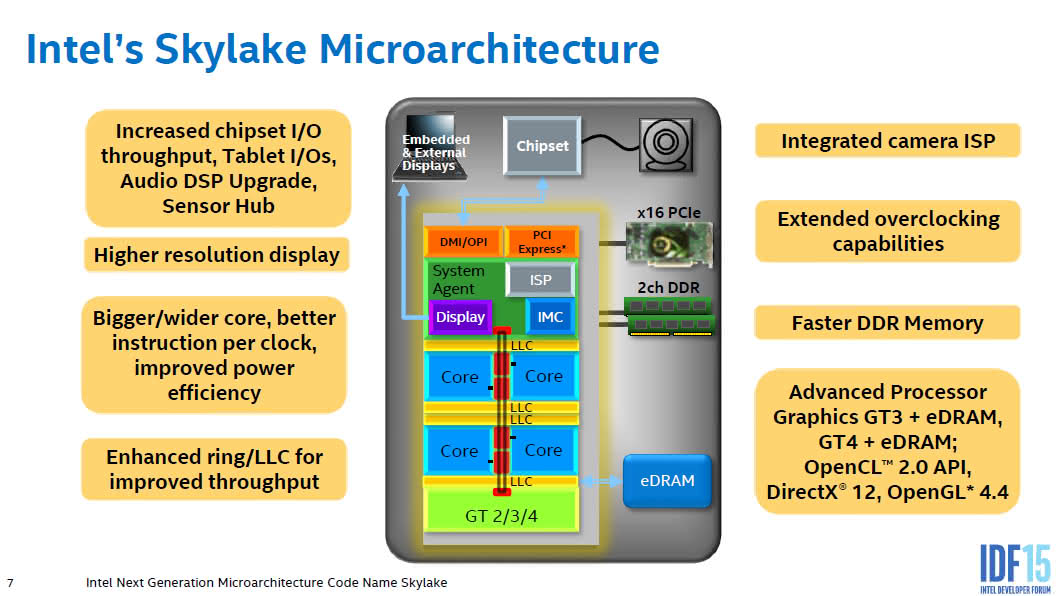

Como mencionamos, a arquitetura Nehalem (Core i7) é baseada na arquitetura usada pelo processador Core 2 Duo, adicionando alguns aprimoramentos na maneira como as instruções fluem dentro do processador. Nesta página descreveremos esses aprimoramentos.

O processador Core 2 Duo, a propósito, é baseado na arquitetura do Pentium M, que por sua vez é baseada na arquitetura usada pelos processadores Pentium III. Todos esses processadores são de 6ª geração (se você rodar a instrução CPUID todos eles retornarão “6” no campo “Família”). O Pentium 4 era um processador Intel de 7ª geração usando uma microarquitetura completamente diferente – os processadores Core 2 e Core i7 não têm nada a ver com o Pentium 4. Você pode achar estranho um fabricante usar em um produto novo uma arquitetura “antiga”, mas é exatamente isto o que aconteceu (a microarquitetura “antiga” provou ser mais eficiente do que a arquitetura “nova”).

Na Figura 5 você pode entender a genealogia da microarquitetura Nehalem. Nós também adicionamos os principais aprimoramentos trazidos por cada novo processador; cada processador tem todos os recursos do processador anterior mais os aprimoramentos mencionados. Claro que cada processador traz outros recursos; nós listamos apenas os recursos mais importantes.

Figura 5: Árvore genealógica da microarquitetura Nehalem.

Para entender os aprimoramentos trazidos por esta nova microarquitetura você precisa lembrar que os programas são escritos usando instruções x86 (também chamadas “macro-ops” ou simplesmente “instruções”), que não são entendidas pelas unidades de execução do processador. Elas precisam primeiro ser decodificadas em microinstruções (também chamadas “micro-op” ou “µop”). Esta arquitetura híbrida CISC/RISC foi introduzida pelo Pentium Pro: o processador recebe instruções x86 (CISC), mas executa microinstruções proprietárias (RISC).

A microarquitetura Core, usada nos processadores Core 2, introduziu o conceito de fusão de instruções (“macro-fusion”), que é a capacidade de combinar duas instruções x86 dentro de apenas uma microinstrução. Isto aumenta o desempenho e diminui o consumo do processador, já que ele executará apenas uma microinstrução em vez de duas. Este esquema, no entanto, é limitado a instruções de desvio condicional e de comparação (ou seja, instruções CMP, TEST e Jcc).

A microarquitetura Nehalem aumenta a capacidade da fusão de instruções de duas formas. Primeiro adicionando suporte a várias instruções condicionais que não poderiam ser fundidas nos processadores Core 2. Segundo, nos processadores baseados na microarquitetura Nehalem a fusão de instruções é usada nos modos de 32 bits e de 64 bits, enquanto que nos processadores Core 2 a fusão de instruções funciona apenas quando o processador está trabalhando no modo de 32 bits.

A microarquitetura Core adicionou um detector de laços (“Loop Stream Detector”), basicamente um pequeno cache de 18 instruções entre as unidades de busca e de decodificação do processador. Quando o processador está executando um laço de repetição (mais conhecido como “loop”, parte de um programa que se repete várias vezes) o processador não precisa buscar as instruções requeridas novamente do cache L1 de instruções: elas já estão próximas da unidade de decodificação. Além disso, o processador desliga as unidades de busca e de previsão de desvio quando detecta a execução de um laço, fazendo com que o processador consuma menos energia.

Nos processadores baseados na microarquitetura Nehalem este pequeno cache foi movido para após da unidade de decodificação de instruções. Portanto, em vez de armazenar instruções x86 como nos processadores Core 2, este cache guarda até 28 microinstruções (micro-ops). Isto faz com que exista um aumento de desempenho quando o processador está executando um laço de repetição, já que agora ele não precisa decodificar as instruções presentes no laço: elas já estarão decodificadas dentro deste pequeno cache. Além disso, o processador pode agora desligar a unidade de decodificação de instruções além das unidades de busca e previsão de desvio quando detecta a execução de um laço, fazendo com que o processador economize ainda mais energia.

Figura 6: Localização do detector de laços nos processadores Core e Nehalem.

A configuração das unidades de execução da microarquitetura Nehalem pode ser vista na Figura 7, sendo bastante similar à configuração usada na microarquitetura Core.

Figura 7: Portas de despacho e unidades de execução.

A microarquitetura Nehalem adicionou também dois buffers extras: um segundo Buffer de Tradução de Endereços (TLB, Translation Look-aside Buffer) com 512 entradas e um segundo Buffer de Desvios (BTB, Branch Target Buffer). A adição desses dois buffers aumenta o desempenho do processador.

O TLB é uma tabela usada pelo circuito de memória virtual para conversões entre endereços físicos e endereços virtuais. A memória virtual é uma técnica onde o processador simula mais memória RAM em um arquivo no disco rígido (chamado arquivo de troca) para permitir que o micro continue operando mesmo quando não há memória RAM suficiente disponível (o processador pega o que está na memória RAM, armazena neste arquivo de troca e então libera espaço na memória para uso).

A previsão de desvios é um circuito que tenta “adivinhar” os próximos passos de um programa, carregando para dentro do processador as instruções que ele acha que o processador tentará carregar. Se ele estiver certo, o processador não perderá tempo carregando essas instruções da memória, já que elas já estarão dentro do processador. Aumentando o tamanho desse buffer (ou adicionando um segundo buffer, no caso dos processadores baseados na microarquitetura Nehalem) permite que este circuito carregue antecipadamente ainda mais instruções, aumentando o desempenho do processador.

.thumb.jpeg.5d29737306dd5ef11d0c5013c75250a6.jpeg)

Respostas recomendadas

Crie uma conta ou entre para comentar

Você precisa ser um usuário para fazer um comentário

Criar uma conta

Crie uma nova conta em nossa comunidade. É fácil!

Crie uma nova contaEntrar

Já tem uma conta? Faça o login.

Entrar agora