Aprimoramentos no Pipeline do Processador

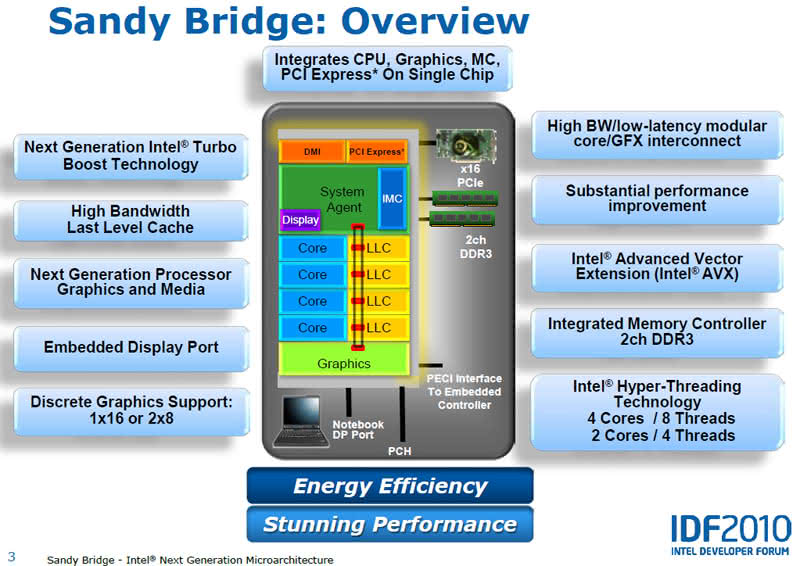

Vamos começar nossa jornada falando da nova maneira como as instruções são processadas na microarquitetura Sandy Bridge.

Existem quatro decodificadores de instruções, o que significa que o processador pode decodificar até quatro instruções por pulso de clock. Esses decodificadores são responsáveis por decodificar instruções IA32 (x86) em microinstruções RISC (µops), que são usadas internamente pelas unidades de execução do processador. Assim como ocorre em outros processadores da Intel, a microarquitetura Sandy Bridge suporta tanto fusão de instruções (“macro-fusion”) quanto fusão de microinstruções (“micro-fusion”). A fusão de instruções permite que o processador decodifique duas instruções x86 relacionadas em apenas uma, enquanto a fusão de microinstruções permite que duas microinstruções relacionadas possam ser fundidas em apenas uma. Obviamente o objetivo dessas tecnologias é aumentar o desempenho.

O que é completamente novo é a adição de um cache de microinstruções decodificadas capaz de armazenar 1.536 microinstruções (o que equivale mais ou menos 6 kB). A Intel chama este cache de “cache L0”. A ideia é óbvia. Quando o programa em execução entra em “loop” (ou seja, precisa repetir a execução de um grupo de instruções várias vezes), o processador não precisa decodificar novamente as instruções x86: elas já estão decodificadas no cache, o que economiza tempo e aumenta o desempenho. De acordo com a Intel, este cache apresenta uma taxa de acerto de 80%, ou seja, o cache é usado pelo menos 80% do tempo.

Agora você pode estar se perguntando se esta não é a mesma ideia usada na microarquitetura Netburst (processadores Pentium 4), que tinha um cache de código (“trace cache”) que também armazenava microinstruções decodificadas. Um cache de código trabalha de forma diferente de um cache de microinstruções: ele armazena as instruções na mesma ordem em que elas foram originalmente executadas. Desta maneira, quando um programa atinge um loop que precisa ser executado, digamos, 10 vezes, o cache de código armazenará as mesmas instruções 10 vezes. Portanto, há muitas instruções repetidas no cache de código, o que não acontece com o cache de microinstruções, que armazena apenas instruções decodificadas individuais.

Quando o cache de microinstruções é usado, o processador coloca o cache de instruções L1 e os decodificadores para “dormir”, o que faz o processador economizar energia e dissipar menos calor.

A unidade de previsão de desvio foi redesenhada e o tamanho do buffer de destino de desvio (Branch Target Buffer ou BTB) foi dobrado em relação à arquitetura Nehalem, além de agora usar uma técnica de compressão que permite que ainda mais dados sejam armazenados. A previsão de desvios é um circuito que tenta “adivinhar” os próximos passos de um programa, carregando para dentro do processador as instruções que ele acha que o processador tentará carregar. Se ele estiver certo, o processador não perderá tempo carregando essas instruções da memória, já que elas já estarão dentro do processador. Aumentando o tamanho desse buffer permite que este circuito carregue antecipadamente ainda mais instruções, aumentando o desempenho do processador.

O agendador usado na microarquitetura Sandy Bridge é similar ao usado na microarquitetura Nehalem, com seis portas de despacho, três delas usadas pelas unidades de execução e três usadas pelas unidades de memória.

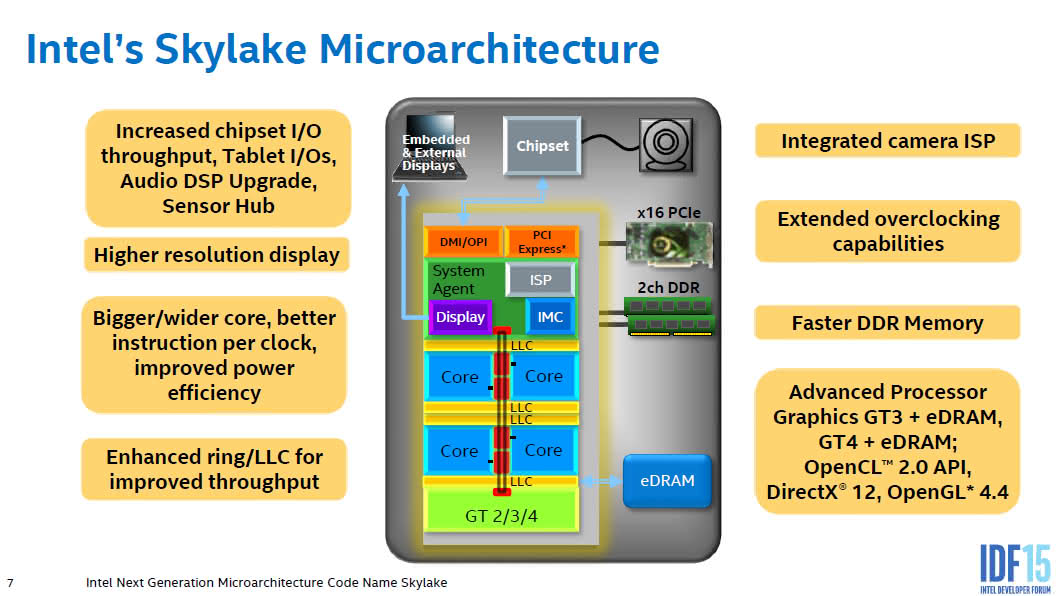

Embora esta configuração seja a mesma, a microarquitetura Sandy Bridge tem mais unidades de execução: enquanto a microarquitetura Nehalem tem 12, a Sandy Bridge tem 15, ver Figura 2. De acordo com a Intel, elas foram redesenhadas para aumentar o desempenho de operações envolvendo números de ponto flutuante (operações matemáticas).

Figura 2: Unidades de execução (configuração padrão)

Cada unidade de execução é conectada ao agendador de instruções usando um caminho de dados de 128 bits. De modo a executar as novas instruções AVX, que trabalham com dados de 256 bits, em vez de adicionar caminhos de dados de 256 bits e unidades de 256 bits ao processador, duas unidades de execução são “agrupadas” (ou seja, usadas ao mesmo tempo), como você pode ver na Figura 3.

Figura 3: Unidades de execução (quando executando instruções AVX)

Após a execução de uma instrução, ela não é copiada de volta para o buffer de reordenamento como acontecia nas arquiteturas anteriores da Intel: o processador apenas indicada que a instrução terminou de ser executada em uma lista. Isto faz com que o processador economize bits e aumente sua eficiência.

Outra diferença está nas portas de memória. A microarquitetura Nehalem tem uma unidade de carga, uma unidade de armazenamento de endereços e uma unidade de armazenamento de dados, cada uma conectada a uma porta de despacho individual. Isto significa que processadores baseados na microarquitetura Nehalem podem carregar do cache L1 de dados 128 bits de dados por pulso de clock.

Na microarquitetura Sandy Bridge, as unidades de carga e armazenamento de endereços podem ser usadas como uma unidade de carga ou como uma unidade de armazenamento de endereços. Esta mudança permite que duas vezes mais dados possam ser carregados do cache L1 de dados por pulso de clock (usando duas unidades de 128 bits ao mesmo tempo em vez de apenas uma), aumentado assim o desempenho. Desta maneira, os processadores Sandy Bridge podem carregar 256 bits de dados do cache L1 de dados por pulso de clock.

Figura 4: Microarquitetura Sandy Bridge

Respostas recomendadas

Crie uma conta ou entre para comentar

Você precisa ser um usuário para fazer um comentário

Criar uma conta

Crie uma nova conta em nossa comunidade. É fácil!

Crie uma nova contaEntrar

Já tem uma conta? Faça o login.

Entrar agora