## LM4780 Overture<sup>™</sup> Audio Power Amplifier Series Stereo 60W, Mono 120W Audio Power Amplifier with **Mute**

## **General Description**

The LM4780 is a stereo audio amplifier capable of typically delivering 60W per channel of continuous average output power into an  $8\Omega$  load with less than 0.5% THD+N from 20Hz - 20kHz.

The LM4780 is fully protected utilizing National's Self Peak Instantaneous Temperature (°Ke) (SPiKe<sup>™</sup>) protection circuitry. SPiKe provides a dynamically optimized Safe Operating Area (SOA). SPiKe protection completely safeguards the LM4780's outputs against over-voltage, under-voltage, overloads, shorts to the supplies or GND, thermal runaway and instantaneous temperature peaks. The advanced protection features of the LM4780 places it in a class above discrete and hybrid amplifiers.

Each amplifier of the LM4780 has an independent smooth transition fade-in/out mute.

The LM4780 can easily be configured for bridge or parallel operation for 120W mono solutions.

### **Key Specifications**

- Output Power/Channel with 0.5% THD+N, 1kHz into 80 60W (typ)

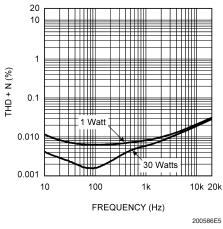

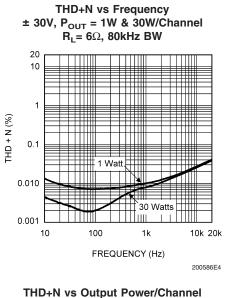

- THD+N at 2 x 30W into 8Ω (20Hz 20kHz) 0.03% (typ)

- THD+N at 2 x 30W into 6Ω (20Hz 20kHz) 0.05% (typ)

- THD+N at 2 x 30W into 4Ω (20Hz 20kHz) 0.07% (typ)

- Mute Attenuation 110dB (typ) 85dB (min)

- PSRB

- Slew Rate

### **Features**

- SPiKe Protection

- Low external component count

- Quiet fade-in/out mute mode

- Wide supply range: 20V 84V

- Signal-to-Noise Ratio  $\geq$  97dB (ref. to P<sub>O</sub> = 1W)

## Applications

- Audio amplifier for component stereo

- Audio amplifier for compact stereo

- Audio amplifier for self-powered speakers

- Audio amplifier for high-end and HD TVs

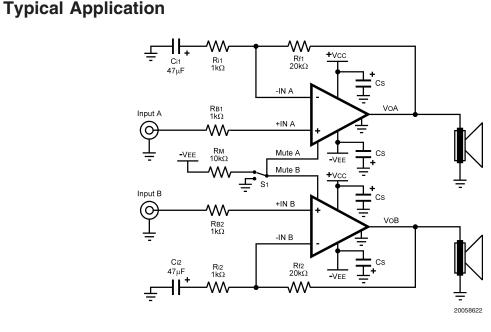

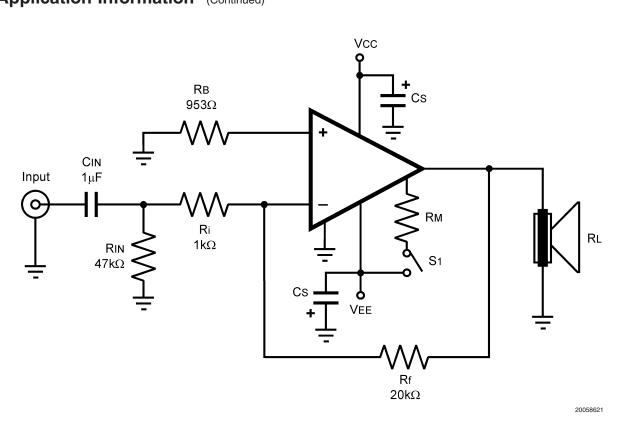

FIGURE 1. Typical Audio Amplifier Application Circuit

SPiKe™ Protection and Overture™ are trademarks of National Semiconductor Corporation

#### July 2003

19V/µs (typ)

## Absolute Maximum Ratings (Notes 1,

#### 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage  V <sup>+</sup>   +  V <sup>-</sup> |                                         |

|----------------------------------------------------|-----------------------------------------|

| (No Signal)                                        | 94V                                     |

| Supply Voltage  V <sup>+</sup>   +  V <sup>-</sup> |                                         |

| (Input Signal)                                     | 84V                                     |

| Common Mode Input Voltage                          | (V <sup>+</sup> or V <sup>-</sup> ) and |

|                                                    | $ V^+  +  V^-  \le 80V$                 |

| Differential Input Voltage (Note 13)               | 60V                                     |

| Output Current                                     | Internally Limited                      |

| Power Dissipation (Note 3)                         | 125W                                    |

| ESD Susceptability (Note 4)                        | 3.0kV                                   |

| ESD Susceptability (Note 5)                        | 200V                                    |

| Junction Temperature $(T_{JMAX})$ (Note 9)         | 150°C                                   |

|                                                    |                                         |

| Soldering Information   |                 |

|-------------------------|-----------------|

| TA Package (10 seconds) | 260°C           |

| Storage Temperature     | -40°C to +150°C |

| Thermal Resistance      |                 |

| $\theta_{JA}$           | 30°C/W          |

| θ <sub>JC</sub>         | 0.8°C/W         |

## Operating Ratings (Notes 1, 2)

Temperature Range

| $T_{MIN} \le T_A \le T_{MAX}$                      | $-20^{\circ}C \leq T_A \leq +85^{\circ}C$ |

|----------------------------------------------------|-------------------------------------------|

| Supply Voltage  V <sup>+</sup>   +  V <sup>-</sup> | $20V \leq V_{\text{TOTAL}} \leq 84V$      |

**Note:** Operation is guaranteed up to 84V; however, distortion may be introduced from **SPiKe** protection circuitry if proper thermal considerations are not taken into account. Refer to the **Thermal Considerations** section for more information.

### Electrical Characteristics (Notes 1, 2)

The following specifications apply for V<sup>+</sup> = +35V, V<sup>-</sup> = -35V, I<sub>MUTE</sub> = -1mA and R<sub>L</sub> = 8 $\Omega$  unless otherwise specified. Limits apply for T<sub>A</sub> = 25°C.

| Symbol                                                                                                                                                     | Parameter                                 | Conditions                                                                         | LM4780   |              | Units     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------|----------|--------------|-----------|

|                                                                                                                                                            |                                           |                                                                                    | Typical  | Limit        | (Limits)  |

|                                                                                                                                                            |                                           |                                                                                    | (Note 6) | (Notes 7, 8) |           |

| V <sup>+</sup>   +  V <sup>-</sup>                                                                                                                         | Power Supply Voltage (Note                | GND – V⁻ ≥ 9V                                                                      | 18       | 20           | V (min)   |

|                                                                                                                                                            | 10)                                       |                                                                                    |          | 84           | V (max)   |

| A <sub>M</sub>                                                                                                                                             | Mute Attenuation                          | I <sub>MUTE</sub> = 0mA                                                            | 110      | 80           | dB (min)  |

|                                                                                                                                                            |                                           | THD+N = 0.5% (max)                                                                 |          |              |           |

|                                                                                                                                                            |                                           | f = 1kHz; f = 20kHz                                                                |          |              |           |

| Po                                                                                                                                                         | Output Power (RMS)                        | $ V^+  =  V^-  = 25V, R_L = 4\Omega$                                               | 55       | 50           | W (min)   |

|                                                                                                                                                            |                                           | $ V^+  =  V^-  = 30V, R_L = 6\Omega$                                               | 55       | 50           | W (min)   |

| $\frac{P_{O}}{P_{O}}$ $\frac{P_{O}}{THD+N}$ $\frac{X_{talk}}{P_{O}}$ $\frac{SR}{I_{DD}}$ $\frac{V_{OS}}{I_{B}}$ $\frac{I_{O}}{V_{OD}}$ $\frac{PSRR}{CMRR}$ |                                           | $ V^+  =  V^-  = 35V, R_L = 8\Omega$                                               | 60       | 50           | W (min)   |

|                                                                                                                                                            |                                           | $P_{O} = 30W, f = 20Hz - 20kHz$                                                    |          |              |           |

|                                                                                                                                                            | Total Harmonia Distortion                 | $A_V = 26 dB$                                                                      |          |              |           |

| THD+N                                                                                                                                                      | Total Harmonic Distortion +<br>Noise      | $ V^+  =  V^-  = 25V, R_L = 4\Omega$                                               | 0.07     |              | %         |

|                                                                                                                                                            |                                           | $ V^+  =  V^-  = 30V, R_L = 6\Omega$                                               | 0.05     |              | %         |

|                                                                                                                                                            |                                           | $ V^+  =  V^-  = 35V, R_L = 8\Omega$                                               | 0.03     |              | %         |

| v                                                                                                                                                          | Channel Separation (Note 11)              | $P_{O} = 10W, f = 1kHz$                                                            | 70       |              | dB        |

| ∧talk                                                                                                                                                      | Channel Separation (Note 11)              | $P_{O} = 10W, f = 10kHz$                                                           | 72       |              | dB        |

| SR                                                                                                                                                         | Slew Rate                                 | $V_{IN} = 2.0V_{P-P}, t_{RISE} = 2ns$                                              | 19       | 8            | V/µs (min |

| I <sub>DD</sub>                                                                                                                                            | Total Quiescent Power                     | $V_{CM} = 0V,$                                                                     | 110      | 170          | mA (max   |

|                                                                                                                                                            | Supply Current                            | $V_{O} = 0V, I_{O} = 0A$                                                           |          |              |           |

| V <sub>os</sub>                                                                                                                                            | Input Offset Voltage                      | $V_{CM} = 0V, I_O = 0mA$                                                           | 1        | 10           | mV (max)  |

|                                                                                                                                                            | Input Bias Current                        | $V_{CM} = 0V, I_O = 0mA$                                                           | 0.2      | 1            | µA (max)  |

| lo                                                                                                                                                         | Output Current Limit                      | $ V^+  =  V^-  = 20V, t_{ON} = 10ms$                                               | 11.5     | 7            | A (min)   |

| V <sub>OD</sub>                                                                                                                                            | Output Dropout Voltage                    | V <sup>+</sup> - V <sub>O</sub>  , V <sup>+</sup> = 28V, I <sub>O</sub> = +100mA   | 1.6      | 2.0          | V (max)   |

|                                                                                                                                                            | (Note 12)                                 | IV <sup>-</sup> - V <sub>O</sub> I, V <sup>-</sup> = -28V, I <sub>O</sub> = -100mA | 2.5      | 3.0          | V (max)   |

|                                                                                                                                                            |                                           | $V^+ = 40V$ to 20V, $V^- = -40V$ ,                                                 | 120      | 95           | dB (min)  |

| DODD                                                                                                                                                       | Power Supply Rejection Ratio<br>(Note 15) | $V_{CM} = 0V, I_O = 0mA$                                                           |          | 85           |           |

| LOKK                                                                                                                                                       |                                           | $V^+ = 40V, V^- = -40V$ to -20V,                                                   | 105      | 85           | dB (min)  |

|                                                                                                                                                            |                                           | $V_{CM} = 0V, I_O = 0mA$                                                           | 105      |              |           |

| CMRR                                                                                                                                                       | Common Mode Rejection Ratio               | $V^+ = 60V$ to 20V, $V^- = -20V$ to -60V,                                          | 110      | 85           | dB (min)  |

|                                                                                                                                                            | (Note 15)                                 | $V_{CM} = 20V$ to -20V, $I_{O} = 0mA$                                              |          |              |           |

#### Electrical Characteristics (Notes 1, 2) (Continued)

The following specifications apply for V<sup>+</sup> = +35V, V<sup>-</sup> = -35V, I<sub>MUTE</sub> = -1mA and R<sub>L</sub> = 8 $\Omega$  unless otherwise specified. Limits apply for T<sub>A</sub> = 25°C.

| Symbol           | Parameter                  | Conditions                                             | LN       | LM4780       |                                                       |

|------------------|----------------------------|--------------------------------------------------------|----------|--------------|-------------------------------------------------------|

|                  |                            |                                                        | Typical  | Limit        | (Limits)                                              |

|                  |                            |                                                        | (Note 6) | (Notes 7, 8) |                                                       |

| A <sub>VOL</sub> | Open Loop Voltage Gain     | $R_L = 2k\Omega, \Delta V_O = 40V$                     | 115      | 90           | dB (min)                                              |

| GBWP             | Gain Bandwidth Product     | $f_{IN} = 100 \text{kHz}, V_{IN} = 50 \text{mV}_{RMS}$ | 8        | 2            | MHz (min)                                             |

| e <sub>IN</sub>  | Input Noise                | IHF-A-Weighting Filter,                                | 2.0      | 10           | μV (max)                                              |

|                  |                            | $R_{IN} = 600\Omega$ (Input Referred)                  |          |              |                                                       |

|                  |                            | $P_{O} = 1W_{RMS}$ ; A-Weighted Filter                 | 97       |              | dB                                                    |

| SNR              | Signal-to-Noise Ratio      | $f_{IN} = 1 \text{kHz}, R_S = 25\Omega$                | 57       |              | uD                                                    |

| SINN             | Signal-to-Noise Hallo      | $P_{O} = 50W_{RMS}$ ; A-Weighted Filter                | 114      |              | 114                                                   |

|                  |                            | $f_{IN} = 1 \text{kHz}, R_S = 25 \Omega$               | 114      |              | D dB (min)<br>MHz (min)<br>μV (max)<br>dB<br>dB<br>dB |

| IMD              | Intermodulation Distortion | 60Hz, 7kHz, 4:1 (SMPTE)                                | 0.004 %  | %            |                                                       |

|                  |                            | 60Hz, 7kHz, 1:1 (SMPTE)                                | 0.009    |              | %                                                     |

Note 1: All voltages are measured with respect to the ground pins, unless otherwise specified.

**Note 2:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given; however, the typical value is a good indication of device performance.

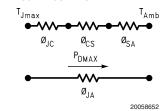

**Note 3:** The maximum power dissipation must be de-rated at elevated temperatures and is dictated by  $T_{JMAX}$ ,  $\theta_{JC}$ , and the ambient temperature  $T_A$ . The maximum allowable power dissipation is  $P_{DMAX} = (T_{JMAX} - T_A)/\theta_{JC}$  or the number given in the Absolute Maximum Ratings, whichever is lower. For the LM4780,  $T_{JMAX} = 150^{\circ}C$  and the typical  $\theta_{JC}$  is 0.8°C/W. Refer to the Thermal Considerations section for more information.

Note 4: Human body model, 100pF discharged through a 1.5k $\Omega$  resistor.

Note 5: Machine Model: a 220pF - 240pF discharged through all pins.

Note 6: Typical specifications are measured at 25°C and represent the parametric norm.

Note 7: Tested limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 8: Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

Note 9: The maximum operating junction temperature is 150°C. However, the instantaneous Safe Operating Area temperature is 250°C.

**Note 10:**  $V^-$  must have at least - 9V at its pin with reference to GND in order for the under-voltage protection circuitry to be disabled. In addition, the voltage differential between V<sup>+</sup> and V<sup>-</sup> must be greater than 14V.

Note 11: Cross talk performance was measured using the demo board shown in the datasheet. PCB layout will affect cross talk. It is recommended that input and output traces be separated by as much distance as possible. Return ground traces from outputs should be independent back to a single ground point and use as wide of traces as possible.

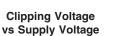

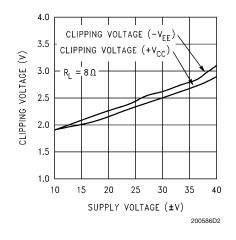

Note 12: The output dropout voltage is defined as the supply voltage minus the clipping voltage. Refer to the Clipping Voltage vs. Supply Voltage graph in the Typical Performance Characteristics section.

Note 13: The Differential Input Voltage Absolute Maximum Rating is based on supply voltages  $V^+ = 40V$  and  $V^- = -40V$ .

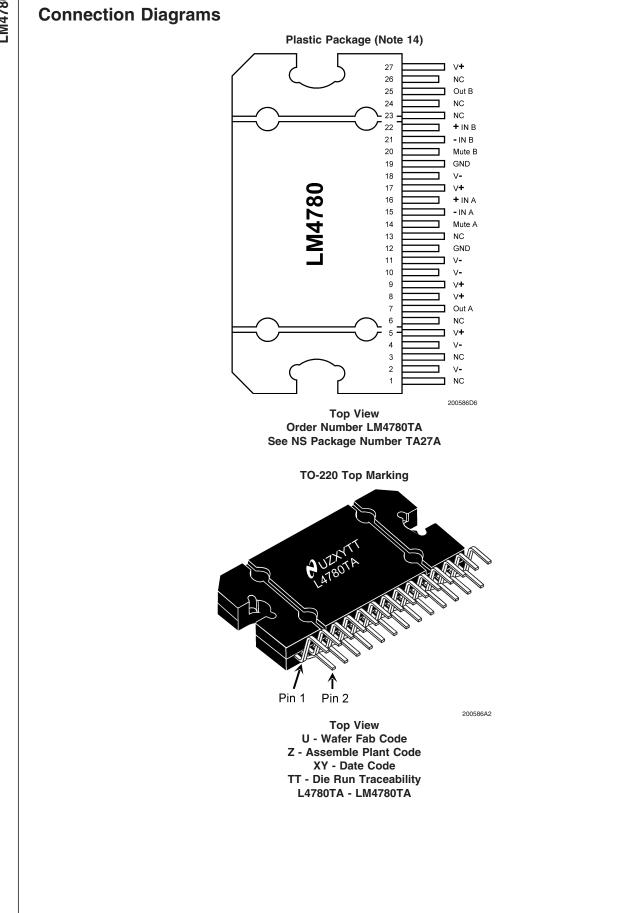

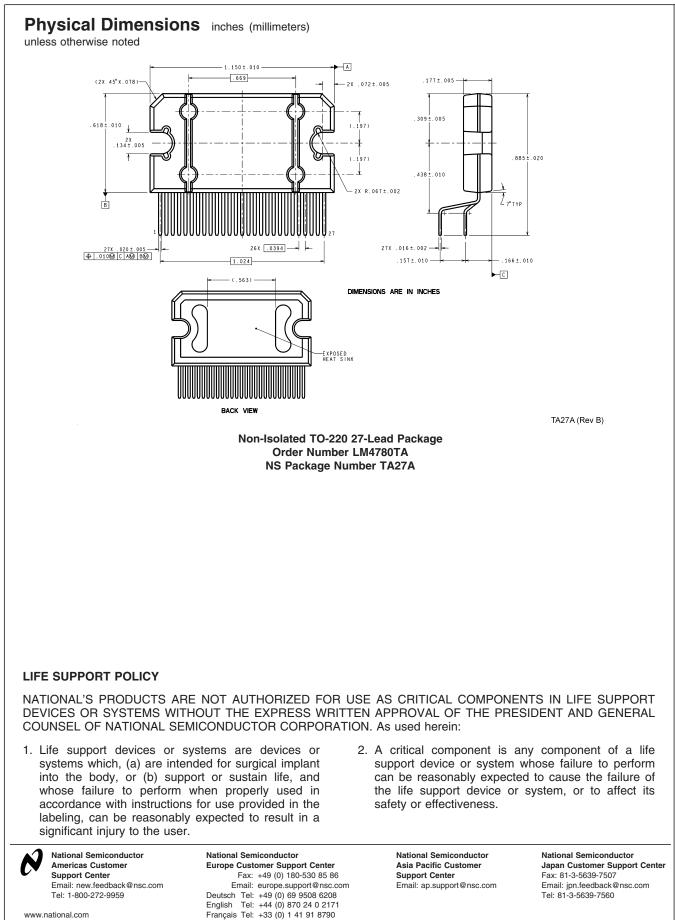

Note 14: The TA27A is a non-isolated package. The package's metal back, and any heat sink to which it is mounted are connected to the V<sup>-</sup> potential when using only thermal compound. If a mica washer is used in addition to thermal compound,  $\theta_{CS}$  (case to sink) is increased, but the heat sink will be electrically isolated from V<sup>-</sup>.

Note 15: DC electrical test.

Note 16: CCIR/ARM: A Practical Noise Measurement Method; by Ray Dolby, David Robinson and Kenneth Gundry, AES Preprint No. 1353 (F-3).

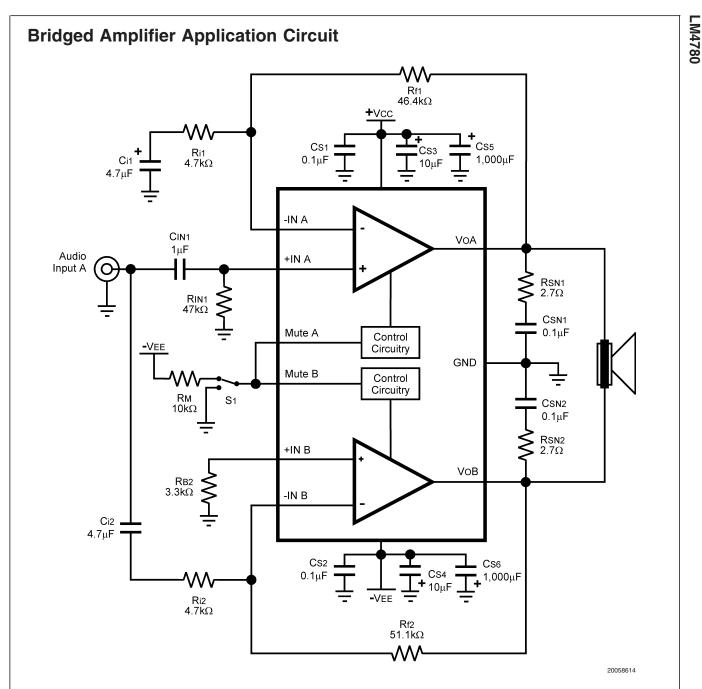

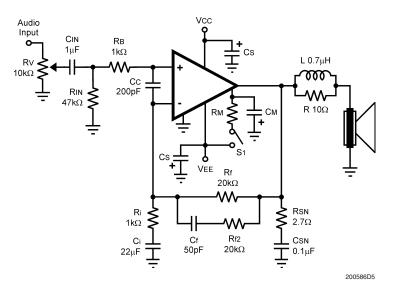

FIGURE 2. Bridged Amplifier Application Circuit

## Parallel Amplifier Application Circuit

20058613

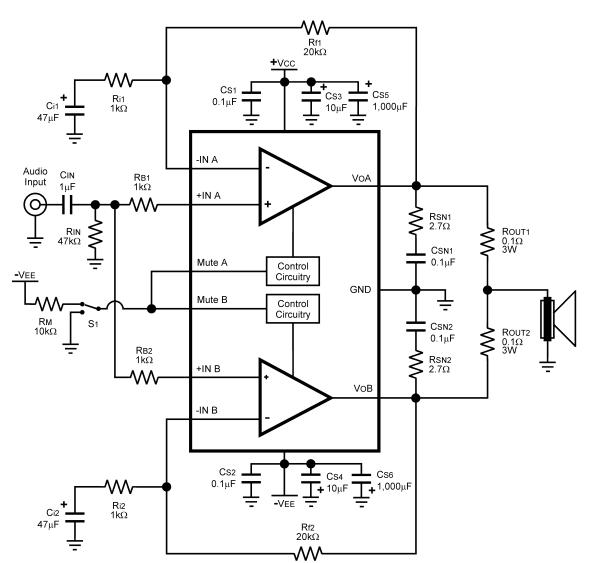

FIGURE 3. Parallel Amplifier Application Circuit

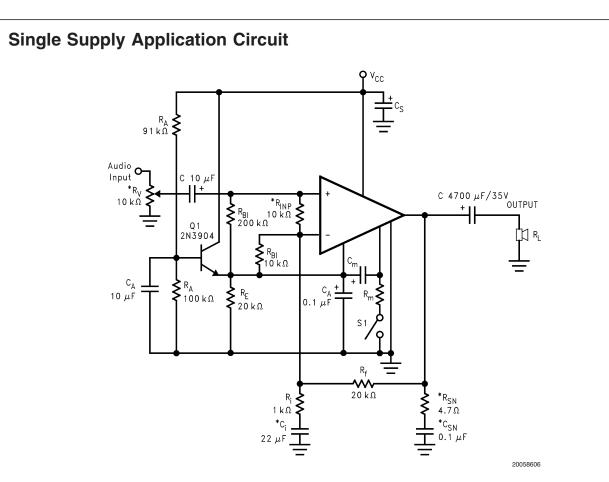

FIGURE 4. Single Supply Amplifier Application Circuit

Note: \*Optional components dependent upon specific design requirements.

## **Auxiliary Amplifier Application Circuit**

FIGURE 5. Special Audio Amplifier Application Circuit

# External Components Description (Figures 1-5)

| Components                                                                      |                  | Functional Description                                                                                                                                            |  |  |

|---------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1                                                                               | R <sub>B</sub>   | Prevents current from entering the amplifier's non-inverting input. This current may pass through to the load                                                     |  |  |

|                                                                                 |                  | during system power down, because of the amplifier's low input impedance when the undervoltage circuitry                                                          |  |  |

|                                                                                 |                  | is off. This phenomenon occurs when the V <sup>+</sup> and V <sup>-</sup> supply voltages are below 1.5V.                                                         |  |  |

| 2                                                                               | R <sub>i</sub>   | Inverting input resistance. Along with R <sub>f</sub> , sets AC gain.                                                                                             |  |  |

| 3 R <sub>f</sub> Feedback resistance. Along with R <sub>i</sub> , sets AC gain. |                  |                                                                                                                                                                   |  |  |

| 4                                                                               | R <sub>f2</sub>  | Feedback resistance. Works with Cf and Rf creating a lowpass filter that lowers AC gain at high                                                                   |  |  |

|                                                                                 | (Note 17)        | frequencies. The -3dB point of the pole occurs when: $(R_f - R_i)/2 = R_f // [1/(2\pi f_c C_f) + R_{f2}]$ for the                                                 |  |  |

|                                                                                 |                  | Non-Inverting configuration shown in Figure 5.                                                                                                                    |  |  |

| 5                                                                               | C <sub>f</sub>   | Compensation capacitor. Works with R <sub>f</sub> and R <sub>f2</sub> to reduce AC gain at higher frequencies.                                                    |  |  |

|                                                                                 | (Note 17)        |                                                                                                                                                                   |  |  |

| 6                                                                               | C <sub>c</sub>   | Compensation capacitor. Reduces the gain at higher frequencies to avoid quasi-saturation oscillations of th                                                       |  |  |

|                                                                                 | (Note 17)        | output transistor. Also suppresses external electromagnetic switching noise created from fluorescent lamps                                                        |  |  |

| 7                                                                               | Ci               | Feedback capacitor which ensures unity gain at DC. Along with $R_i$ also creates a highpass filter at $f_c =$                                                     |  |  |

|                                                                                 | (Note 17)        | $1/(2\pi R_i C_i)$ .                                                                                                                                              |  |  |

| 8                                                                               | Cs               | Provides power supply filtering and bypassing. Refer to the Supply Bypassing application section for prope                                                        |  |  |

| -                                                                               | - 5              | placement and selection of bypass capacitors.                                                                                                                     |  |  |

| 9                                                                               | R <sub>v</sub>   | Acts as a volume control by setting the input voltage level.                                                                                                      |  |  |

| -                                                                               | (Note 17)        |                                                                                                                                                                   |  |  |

| 10                                                                              | R <sub>IN</sub>  | Sets the amplifier's input terminals DC bias point when C <sub>IN</sub> is present in the circuit. Also works with C <sub>IN</sub> to                             |  |  |

| 10                                                                              | (Note 17)        | create a highpass filter at $f_c = 1/(2\pi R_{IN}C_{IN})$ . If the value of $R_{IN}$ is too large, oscillations may be observed of                                |  |  |

|                                                                                 |                  | the outputs when the inputs are floating. Recommended values are $10k\Omega$ to $47k\Omega$ . Refer to <i>Figure 5</i> .                                          |  |  |

| 11                                                                              | C <sub>IN</sub>  | Input capacitor. Prevents the input signal's DC offsets from being passed onto the amplifier's inputs.                                                            |  |  |

|                                                                                 | (Note 17)        |                                                                                                                                                                   |  |  |

| 12                                                                              | R <sub>SN</sub>  | Works with C <sub>SN</sub> to stabilize the output stage by creating a pole that reduces high frequency instabilities.                                            |  |  |

| 12                                                                              | (Note 17)        | works with ogn to stabilize the output stage by creating a pole that reduces high nequency instabilities.                                                         |  |  |

| 13                                                                              | C <sub>SN</sub>  | Works with R <sub>SN</sub> to stabilize the output stage by creating a pole that reduces high frequency instabilities. The                                        |  |  |

| 10                                                                              | (Note 17)        | pole is set at $f_c = 1/(2\pi R_{sN}C_{sN})$ . Refer to Figure 5.                                                                                                 |  |  |

| 14                                                                              | L (Note 17)      | Provides high impedance at high frequencies so that R may decouple a highly capacitive load and reduce                                                            |  |  |

| 14                                                                              |                  | the Q of the series resonant circuit. Also provides a low impedance at low frequencies to short out R and                                                         |  |  |

| 15                                                                              | R (Note 17)      | pass audio signals to the load. Refer to Figure 5.                                                                                                                |  |  |

| 16                                                                              | D                | Provides DC voltage biasing for the transistor Q1 in single supply operation.                                                                                     |  |  |

|                                                                                 | R <sub>A</sub>   |                                                                                                                                                                   |  |  |

| 17                                                                              | C <sub>A</sub>   | Provides bias filtering for single supply operation.                                                                                                              |  |  |

| 18                                                                              | R <sub>INP</sub> | Limits the voltage difference between the amplifier's inputs for single supply operation. Refer to the <b>Clicks</b>                                              |  |  |

|                                                                                 | (Note 17)        | and Pops application section for a more detailed explanation of the function of R <sub>INP</sub> .                                                                |  |  |

| 19                                                                              | R <sub>BI</sub>  | Provides input bias current for single supply operation. Refer to the <b>Clicks and Pops</b> application section for                                              |  |  |

|                                                                                 |                  | a more detailed explanation of the function of R <sub>BI</sub> .                                                                                                  |  |  |

| 20                                                                              | R <sub>E</sub>   | Establishes a fixed DC current for the transistor Q1 in single supply operation. This resistor stabilizes the                                                     |  |  |

|                                                                                 |                  | half-supply point along with C <sub>A</sub> .                                                                                                                     |  |  |

| 21                                                                              | R <sub>M</sub>   | Mute resistance set up to allow 0.5mA to be drawn from each MUTE pin to turn the muting function off.                                                             |  |  |

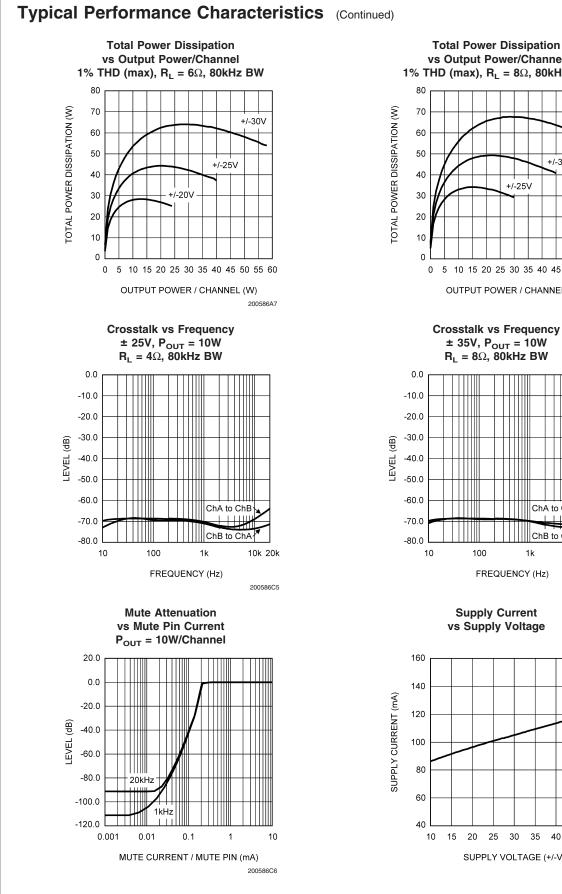

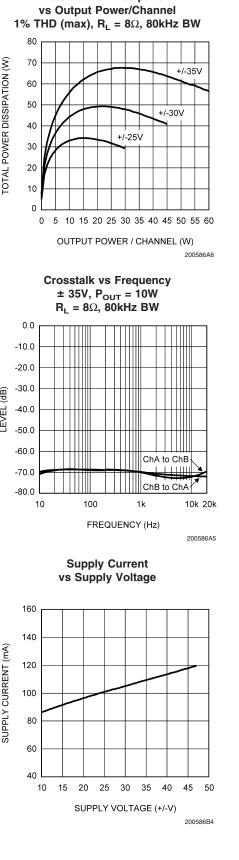

|                                                                                 |                  | $\rightarrow$ R <sub>M</sub> is calculated using: R <sub>M</sub> $\leq$ (IV <sub>EE</sub> I – 2.6V)/I where I $\geq$ 0.5mA. Refer to the Mute Attenuation vs Mute |  |  |

|                                                                                 |                  | Current curves in the Typical Performance Characteristics section.                                                                                                |  |  |

| 22                                                                              | C <sub>M</sub>   | Mute capacitance set up to create a large time constant for turn-on and turn-off muting.                                                                          |  |  |

| 23                                                                              | S <sub>1</sub>   | Mute switch. When open or switched to GND, the amplifier will be in mute mode.                                                                                    |  |  |

| 24                                                                              | R <sub>OUT</sub> | Reduces current flow between outputs that are caused by Gain or DC offset differences between the                                                                 |  |  |

|                                                                                 |                  |                                                                                                                                                                   |  |  |

## OPTIONAL EXTERNAL COMPONENT INTERACTION

The optional external components have specific desired functions. Their values are chosen to reduce the bandwidth and eliminate unwanted high frequency oscillation. They may, however, cause certain undesirable effects when they interact. Interaction may occur when the components produce reactions that are nearly equal to one another. One example is the coupling capacitor,  $C_{\rm C}$ , and the compensa-

## **Typical Performance Characteristics**

tion capacitor,  $C_f$ . These two components are low impedances at certain frequencies. They may couple signals from the input to the output. Please take careful note of basic amplifier component functionality when selecting the value of these components and their placement on a printed circuit board (PCB).

The optional external components shown in *Figure 4* and *Figure 5*, and described above, are applicable in both single and split supply voltage configurations.

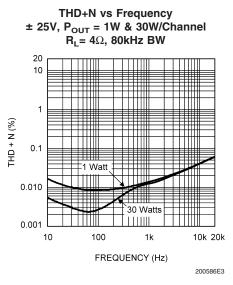

$\pm$  25V, R<sub>L</sub>= 4 $\Omega$ , 80kHz BW

36

## Typical Performance Characteristics (Continued)

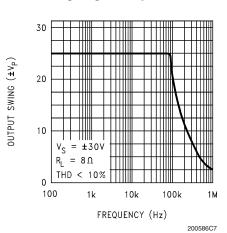

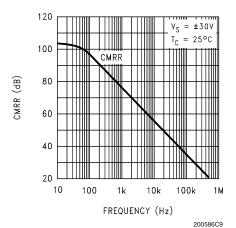

#### Large Signal Response

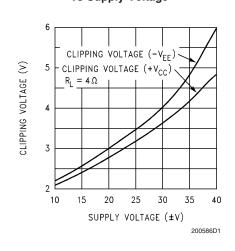

**Rejection Ratio**

Power Supply Rejection Ratio

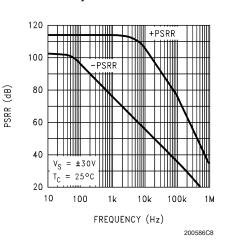

Open Loop Frequency Response

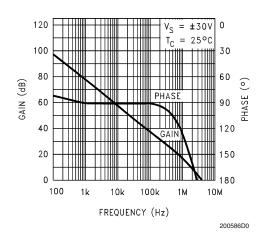

Clipping Voltage vs Supply Voltage

## Typical Performance Characteristics (Continued)

200586E2

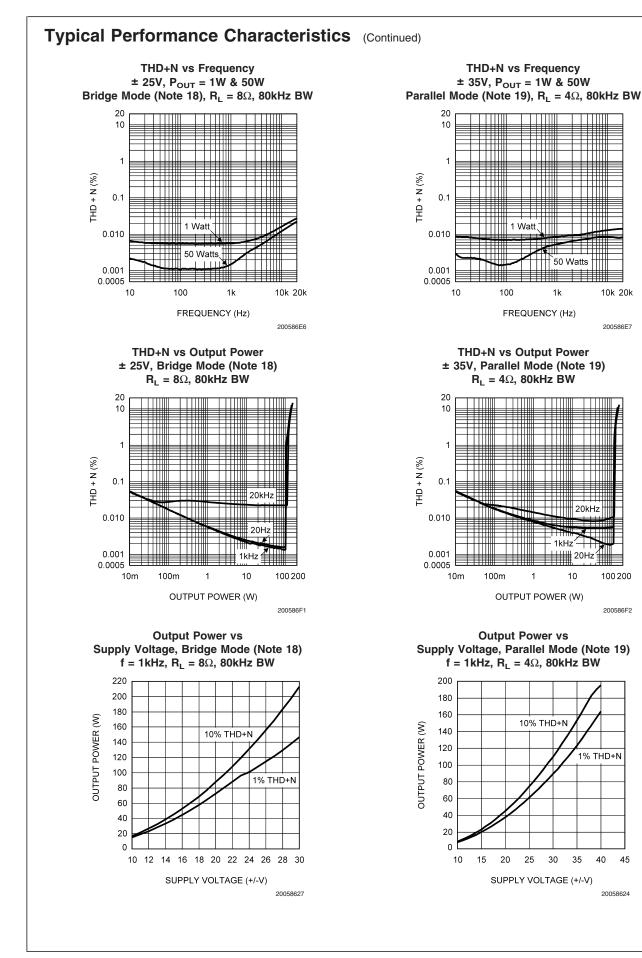

Note 18: Bridge mode graphs were taken using the demo board and inverting the signal to the channel B input.

Note 19: Parallel mode graphs were taken using the demo board and connecting each output through a 0.1 $\Omega$ /3W resistor to the load.

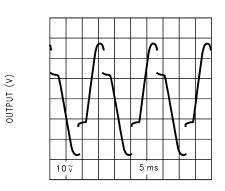

SPiKe Protection Response

TIME (ms)

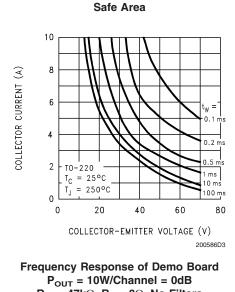

#### The LM4780 is protected from instantaneous peaktemperature stressing of the power transistor array. The Safe Operating graph in the Typical Performance Characteristics section shows the area of device operation where SPiKe Protection Circuitry is not enabled. The SPiKe Protection Response waveform graph shows the waveform distortion when SPiKe is enabled. Please refer to AN-898 for

### more detailed information. THERMAL PROTECTION

large current spikes.

SPiKe PROTECTION

**OVER-VOLTAGE PROTECTION**

The LM4780 has a sophisticated thermal protection scheme to prevent long-term thermal stress of the device. When the temperature on the die exceeds 150°C, the LM4780 shuts down. It starts operating again when the die temperature drops to about 145°C, but if the temperature again begins to rise, shutdown will occur again above 150°C. Therefore, the device is allowed to heat up to a relatively high temperature if the fault condition is temporary, but a sustained fault will cause the device to cycle in a Schmitt Trigger fashion between the thermal shutdown temperature limits of 150°C and 145°C. This greatly reduces the stress imposed on the IC by thermal cycling, which in turn improves its reliability under sustained fault conditions.

The LM4780 contains over-voltage protection circuitry that limits the output current while also providing voltage clamp-

ing. The clamp does not, however, use internal clamping

diodes. The clamping effect is quite the same because the

output transistors are designed to work alternately by sinking

Since the die temperature is directly dependent upon the heat sink used, the heat sink should be chosen so that thermal shutdown is not activated during normal operation. Using the best heat sink possible within the cost and space constraints of the system will improve the long-term reliability of any power semiconductor device, as discussed in the Determining the Correct Heat Sink section.

#### DETERMINING MAXIMUM POWER DISSIPATION

Power dissipation within the integrated circuit package is a very important parameter requiring a thorough understanding if optimum power output is to be obtained. An incorrect maximum power dissipation calculation may result in inadequate heat sinking causing thermal shutdown and thus limiting the output power.

Equation (2) shows the theoretical maximum power dissipation point of each amplifier in a single-ended configuration where  $V_{CC}$  is the total supply voltage.

$$P_{\rm DMAX} = (V_{\rm CC})^2 / 2\pi^2 R_{\rm L}$$

(2)

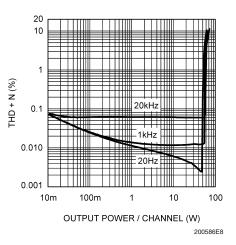

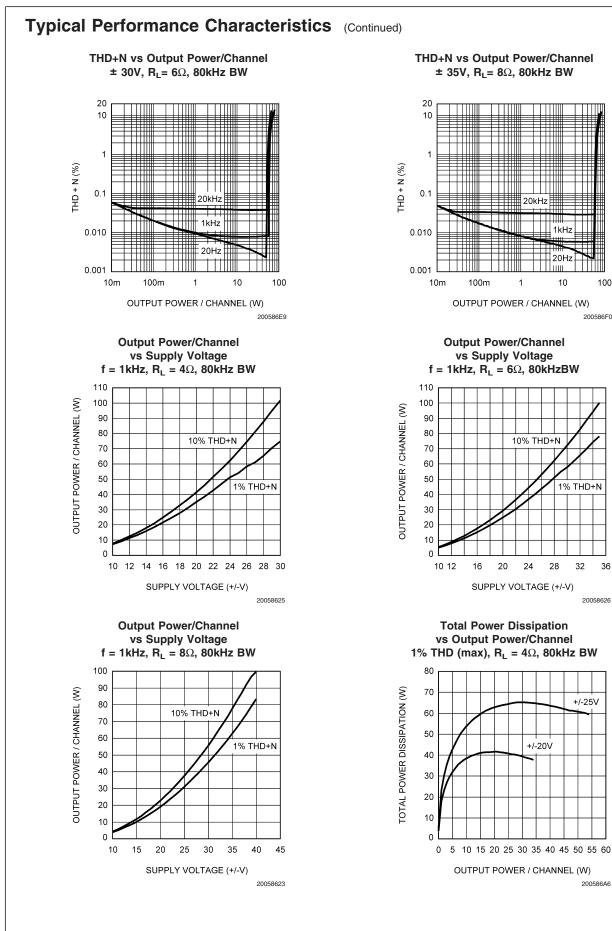

Thus by knowing the total supply voltage and rated output load, the maximum power dissipation point can be calculated. The package dissipation is twice the number which results from Equation (2) since there are two amplifiers in each LM4780. Refer to the graphs of Power Dissipation versus Output Power in the Typical Performance Characteristics section which show the actual full range of power dissipation not just the maximum theoretical point that results from Equation (2).

## **Application Information**

#### MUTE MODE

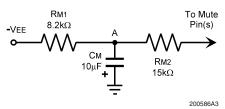

The muting function allows the user to mute the amplifier. This can be accomplished as shown in the Typical Application Circuit. The resistor  $\mathsf{R}_\mathsf{M}$  is chosen with reference to the negative supply voltage and is used in conjunction with a switch. The switch, when opened or switched to GND, cuts off the current flow from the MUTE pins to -V<sub>EE</sub>, thus placing the LM4780 into mute mode. Refer to the Mute Attenuation vs Mute Current curves in the Typical Performance Characteristics section for values of attenuation per current out of each MUTE pin. The resistance  $\mathsf{R}_\mathsf{M}$  is calculated by the following equation:

$$R_{M} \leq (|-V_{EE}| - 2.6V) / I_{MUTE}$$

Where

$$I_{MUTE} \ge 0.5 \text{mA}$$

for each MUTE pin.

The MUTE pins can be tied together so that only one resistor is required for the mute function. The mute resistor value must be chosen so that a minimum of 1mA is pulled through the resistor  $R_{M}$ . This ensures that each amplifier is fully operational. Taking into account supply line fluctuations, it is a good idea to pull out 1mA per MUTE pin or 2mA total if both pins are tied together.

A turn-on MUTE or soft start circuit may also be used during power up. A simple circuit like the one shown below may be used.

The RC combination of  $C_M$  and  $R_{M1}$  may cause the voltage at point A to change more slowly than the -V<sub>EE</sub> supply voltage. Until the voltage at point A is low enough to have 0.5mA of current per MUTE pin flow through R<sub>M2</sub>, the IC will be in mute mode. The series combination of  $R_{M1}$  and  $R_{M2}$ needs to satisfy the mute equation above for all operating voltages or mute mode may be activated during normal operation. For a longer turn-on mute time, a larger time constant,  $\tau = RC = R_{M1}C_M$  (sec), is needed. For the values show above and with the MUTE pins tied together, the LM4780 will enter play mode when the voltage at point A is -17.6V. The voltage at point A is found with Equation (1) below.

$$V_{A}(t) = (V_{f} - V_{O})e^{-t/\tau} \text{ (Volts)}$$

(1)

where:

t = time (sec)

$\tau = RC$  (sec)

$V_o =$  Voltage on C at t = 0 (Volts)

$V_f =$  Final voltage,  $-V_{EE}$  in this circuit (Volts)

#### **UNDER-VOLTAGE PROTECTION**

Upon system power-up, the under-voltage protection circuitry allows the power supplies and their corresponding capacitors to come up close to their full values before turning on the LM4780. Since the supplies have essentially settled to their final value, no DC output spikes occur. At power down, the outputs of the LM4780 are forced to ground before the power supply voltages fully decay preventing transients on the output.

#### DETERMINING THE CORRECT HEAT SINK

The choice of a heat sink for a high-power audio amplifier is made entirely to keep the die temperature at a level such that the thermal protection circuitry is not activated under normal circumstances.

The thermal resistance from the die to the outside air,  $\theta_{JA}$  (junction to ambient), is a combination of three thermal resistances,  $\theta_{JC}$  (junction to case),  $\theta_{CS}$  (case to sink), and  $\theta_{SA}$  (sink to ambient). The thermal resistance,  $\theta_{JC}$  (junction to case), of the LM4780T is 0.8°C/W. Using Thermalloy Thermacote thermal compound, the thermal resistance,  $\theta_{CS}$  (case to sink), is about 0.2°C/W. Since convection heat flow (power dissipation) is analogous to current flow, thermal resistance is analogous to voltage drops, the power dissipation out of the LM4780 is equal to the following:

$$P_{DMAX} = (T_{JMAX} - T_{AMB}) / \theta_{JA}$$

(3)

where  $T_{JMAX}$  = 150°C,  $T_{AMB}$  is the system ambient temperature and  $\theta_{JA}$  =  $\theta_{JC}$  +  $\theta_{CS}$  +  $\theta_{SA}$ .

Once the maximum package power dissipation has been calculated using *Equation (2)*, the maximum thermal resistance,  $\theta_{SA}$ , (heat sink to ambient) in °C/W for a heat sink can be calculated. This calculation is made using *Equation (4)* which is derived by solving for  $\theta_{SA}$  in *Equation (3)*.

$$\theta_{SA} = \left[ \left( \mathsf{T}_{\mathsf{JMAX}} - \mathsf{T}_{\mathsf{AMB}} \right) - \mathsf{P}_{\mathsf{DMAX}} \left( \theta_{\mathsf{JC}} + \theta_{\mathsf{CS}} \right) \right] / \mathsf{P}_{\mathsf{DMAX}} \quad (4)$$

Again it must be noted that the value of  $\theta_{SA}$  is dependent upon the system designer's amplifier requirements. If the ambient temperature that the audio amplifier is to be working under is higher than 25°C, then the thermal resistance for the heat sink, given all other things are equal, will need to be smaller.

#### SUPPLY BYPASSING

The LM4780 has excellent power supply rejection and does not require a regulated supply. However, to improve system performance as well as eliminate possible oscillations, the LM4780 should have its supply leads bypassed with lowinductance capacitors having short leads that are located close to the package terminals. Inadequate power supply bypassing will manifest itself by a low frequency oscillation known as "motorboating" or by high frequency instabilities. These instabilities can be eliminated through multiple bypassing utilizing a large tantalum or electrolytic capacitor (10µF or larger) which is used to absorb low frequency variations and a small ceramic capacitor (0.1µF) to prevent any high frequency feedback through the power supply lines. If adequate bypassing is not provided, the current in the supply leads which is a rectified component of the load current may be fed back into internal circuitry. This signal causes distortion at high frequencies requiring that the supplies be bypassed at the package terminals with an electrolytic capacitor of 470µF or more.

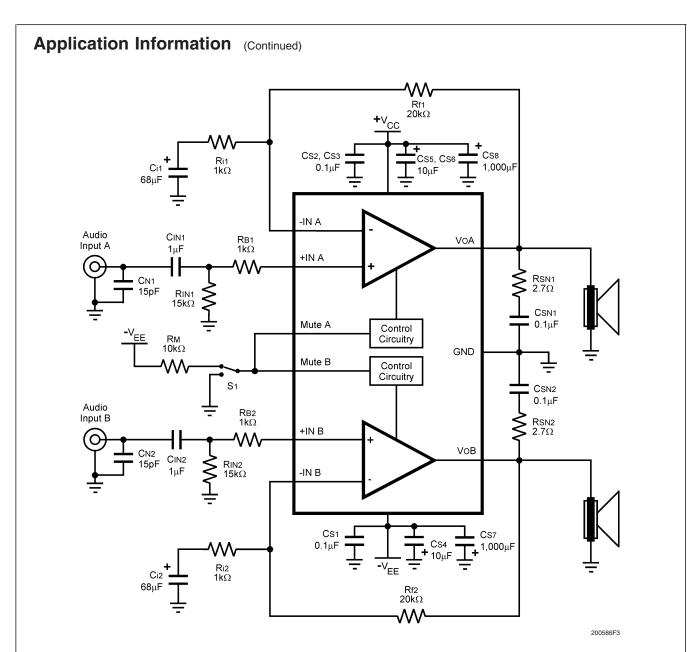

#### **BRIDGED AMPLIFIER APPLICATION**

The LM4780 has two operational amplifiers internally, allowing for a few different amplifier configurations. One of these configurations is referred to as "bridged mode" and involves driving the load differentially through the LM4780's outputs. This configuration is shown in *Figure 2*. Bridged mode operation is different from the classical single-ended amplifier configuration where one side of its load is connected to ground.

A bridge amplifier design has a distinct advantage over the single-ended configuration, as it provides differential drive to the load, thus doubling output swing for a specified supply voltage. Theoretically, four times the output power is possible as compared to a single-ended amplifier under the same conditions. This increase in attainable output power assumes that the amplifier is not current limited or clipped.

A direct consequence of the increased power delivered to the load by a bridge amplifier is an increase in internal power dissipation. For each operational amplifier in a bridge configuration, the internal power dissipation will increase by a factor of two over the single ended dissipation. Thus, for an audio power amplifier such as the LM4780, which has two operational amplifiers in one package, the package dissipation will increase by a factor of four. To calculate the LM4780's maximum power dissipation point for a bridged load, multiply *Equation (2)* by a factor of four.

This value of  $P_{DMAX}$  can be used to calculate the correct size heat sink for a bridged amplifier application. Since the internal dissipation for a given power supply and load is increased by using bridged-mode, the heatsink's  $\theta_{SA}$  will have to decrease accordingly as shown by *Equation (4)*. Refer to the section, **Determining the Correct Heat Sink**, for a more detailed discussion of proper heat sinking for a given application.

#### PARALLEL AMPLIFIER APPLICATION

Parallel configuration is normally used when higher output current is needed for driving lower impedance loads (i.e.  $4\Omega$ or lower) to obtain higher output power levels. As shown in Figure 3, the parallel amplifier configuration consist of designing the amplifiers in the IC to have identical gain, connecting the inputs in parallel and then connecting the outputs in parallel through a small external output resistor. Any number of amplifiers can be connected in parallel to obtain the needed output current or to divide the power dissipation across multiple IC packages. Ideally, each amplifier shares the output current equally. Due to slight differences in gain the current sharing will not be equal among all channels. If current is not shared equally among all channels then the power dissipation will also not be equal among all channels. It is recommended that 0.1% tolerance resistors be used to set the gain (R<sub>i</sub> and R<sub>f</sub>) for a minimal amount of difference in current sharing.

When operating two or more amplifiers in parallel mode the impedance seen by each amplifier is equal to the total load impedance multiplied by the number of amplifiers driving the load in parallel as shown by *Equation (5)* below:

$R_{L(parallel)} = R_{L(total)} * Number of amplifiers \tag{5}$ Once the impedance seen by each amplifier in the parallel configuration is known then Equation (2) can be used with this calculated impedance to find the amount of power dissipation for each amplifier. Total power dissipation (P\_{DMAX}) within an IC package is found by adding up the power dissipation for each amplifier in the IC package. Using the calculated P\_{DMAX} the correct heat sink size can be deter-

mined. Refer to the section, **Determining the Correct Heat Sink**, for more information and detailed discussion of proper heat sinking.

#### SINGLE-SUPPLY AMPLIFIER APPLICATION

The typical application of the LM4780 is a split supply amplifier. But as shown in *Figure 4*, the LM4780 can also be used in a single power supply configuration. This involves using some external components to create a half-supply bias which is used as the reference for the inputs and outputs. Thus, the signal will swing around half-supply much like it swings around ground in a split-supply application. Along with proper circuit biasing, a few other considerations must be accounted for to take advantage of all of the LM4780 functions, like the mute function.

#### **CLICKS AND POPS**

In the typical application of the LM4780 as a split-supply audio power amplifier, the IC exhibits excellent "click" and "pop" performance when utilizing the mute mode. In addition, the device employs Under-Voltage Protection, which eliminates unwanted power-up and power-down transients. The basis for these functions are a stable and constant half-supply potential. In a split-supply application, ground is the stable half-supply potential. But in a single-supply application, the half-supply needs to charge up at the same rate as the supply rail,  $V_{CC}$ . This makes the task of attaining a clickless and popless turn-on more challenging. Any uneven charging of the amplifier inputs will result in output clicks and pops due to the differential input topology of the LM4780.

To achieve a transient free power-up and power-down, the voltage seen at the input terminals should be ideally the same. Such a signal will be common-mode in nature, and will be rejected by the LM4780. In *Figure 4*, the resistor  $R_{\rm INP}$  serves to keep the inputs at the same potential by limiting the voltage difference possible between the two nodes. This should significantly reduce any type of turn-on pop, due to an uneven charging of the amplifier inputs. This charging is based on a specific application loading and thus, the system designer may need to adjust these values for optimal performance.

As shown in *Figure 4*, the resistors labeled R<sub>BI</sub> help bias up the LM4780 off the half-supply node at the emitter of the 2N3904. But due to the input and output coupling capacitors in the circuit, along with the negative feedback, there are two different values of R<sub>BI</sub>, namely 10k $\Omega$  and 200k $\Omega$ . These resistors bring up the inputs at the same rate resulting in a popless turn-on. Adjusting these resistors values slightly may reduce pops resulting from power supplies that ramp extremely quick or exhibit overshoot during system turn-on.

#### PROPER SELECTION OF EXTERNAL COMPONENTS

Proper selection of external components is required to meet the design targets of an application. The choice of external component values that will affect gain and low frequency response are discussed below.

The gain of each amplifier is set by resistors  $R_f$  and  $R_i$  for the non-inverting configuration shown in *Figure 1*. The gain is found by *Equation (6)* below:

$$A_V = 1 + R_f / R_i (V/V)$$

(6)

For best noise performance, lower values of resistors are used. A value of  $1k\Omega$  is commonly used for  $R_i$  and then setting the value of  $R_f$  for the desired gain. For the LM4780 the gain should be set no lower than 10V/V and no higher

than 50V/V. Gain settings below 10V/V may experience instability and using the LM4780 for gains higher than 50V/V will see an increase in noise and THD.

The combination of  $R_i$  with  $C_i$  (see *Figure 1*) creates a high pass filter. The low frequency response is determined by these two components. The -3dB point can be found from *Equation (7)* shown below:

$$_{i} = 1 / (2\pi R_{i}C_{i}) (Hz)$$

(7)

If an input coupling capacitor is used to block DC from the inputs as shown in *Figure 5*, there will be another high pass filter created with the combination of  $C_{IN}$  and  $R_{IN}$ . When using a input coupling capacitor  $R_{IN}$  is needed to set the DC bias point on the amplifier's input terminal. The resulting -3dB frequency response due to the combination of  $C_{IN}$  and  $R_{IN}$  can be found from *Equation (8)* shown below:

$$f_{IN} = 1 / (2\pi R_{IN} C_{IN}) (Hz)$$

(8)

With large values of  $R_{\rm IN}$  oscillations may be observed on the outputs when the inputs are left floating. Decreasing the value of  $R_{\rm IN}$  or not letting the inputs float will remove the oscillations. If the value of  $R_{\rm IN}$  is decreased then the value of  $C_{\rm IN}$  will need to increase in order to maintain the same -3dB frequency response.

#### HIGH PERFORMANCE CONSIDERATIONS

Using low cost electrolytic capacitors in the signal path such as  $C_{\rm IN}$  and  $C_{\rm i}$  (see Figures 1 - 5) will result in very good performance. However, electrolytic capacitors are less linear than other premium capacitors. Higher THD+N performance may be obtained by using high quality polypropylene capacitors in the signal path. A more cost effective solution may be the use of smaller value premium capacitors in parallel with the larger electrolytic capacitors. This will maintain signal quality in the upper audio band where any degradation is most noticeable while also coupling in the signals in the lower audio band for good bass response.

Distortion is introduced as the audio signal approaches the lower -3dB point, determined as discussed in the section above. By using larger values of capacitors such that the -3dB point is well outside of the audio band will reduce this distortion and improve THD+N performance.

Increasing the value of the large supply bypass capacitors will improve burst power output. The larger the supply bypass capacitors the higher the output pulse current without supply droop increasing the peak output power. This will also increase the headroom of the amplifier and reduce THD.

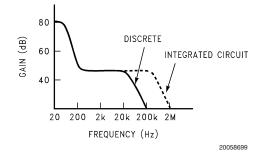

#### SIGNAL-TO-NOISE RATIO

In the measurement of the signal-to-noise ratio, misinterpretations of the numbers actually measured are common. One amplifier may sound much quieter than another, but due to improper testing techniques, they appear equal in measurements. This is often the case when comparing integrated circuit designs to discrete amplifier designs. Discrete transistor amps often "run out of gain" at high frequencies and therefore have small bandwidths to noise as indicated below.

## Application Information (Continued)

Integrated circuits have additional open loop gain allowing additional feedback loop gain in order to lower harmonic distortion and improve frequency response. It is this additional bandwidth that can lead to erroneous signal-to-noise measurements if not considered during the measurement process. In the typical example above, the difference in bandwidth appears small on a log scale but the factor of 10in bandwidth, (200kHz to 2MHz) can result in a 10dB theoretical difference in the signal-to-noise ratio (white noise is proportional to the square root of the bandwidth in a system). In comparing audio amplifiers it is necessary to measure the magnitude of noise in the audible bandwidth by using a "weighting" filter (Note 16). A "weighting" filter alters the frequency response in order to compensate for the average human ear's sensitivity to the frequency spectra. The weighting filters at the same time provide the bandwidth limiting as discussed in the previous paragraph.

In addition to noise filtering, differing meter types give different noise readings. Meter responses include:

- 1. RMS reading,

- 2. average responding,

- 3. peak reading, and

- 4. quasi peak reading.

Although theoretical noise analysis is derived using true RMS based calculations, most actual measurements are taken with ARM (Average Responding Meter) test equipment.

Typical signal-to-noise figures are listed for an A-weighted filter which is commonly used in the measurement of noise. The shape of all weighting filters is similar, with the peak of the curve usually occurring in the 3kHz–7kHz region.

#### LEAD INDUCTANCE

Power op amps are sensitive to inductance in the output leads, particularly with heavy capacitive loading. Feedback to the input should be taken directly from the output terminal, minimizing common inductance with the load.

Lead inductance can also cause voltage surges on the supplies. With long leads to the power supply, energy is stored in the lead inductance when the output is shorted. This energy can be dumped back into the supply bypass capacitors when the short is removed. The magnitude of this transient is reduced by increasing the size of the bypass capacitor near the IC. With at least a  $20\mu$ F local bypass, these voltage surges are important only if the lead length exceeds a couple feet (>1µH lead inductance). Twisting together the supply and ground leads minimizes the effect.

#### PHYSICAL IC MOUNTING CONSIDERATIONS

Mounting of the package to a heat sink must be done such that there is sufficient pressure from the mounting screws to insure good contact with the heat sink for efficient heat flow. Over tightening the mounting screws will cause the package to warp reducing contact area with the heat sink. Less contact with the heat sink will increase the thermal resistance from the package case to the heat sink ( $\theta_{\text{CS}}$ ) resulting in higher operating die temperatures and possible unwanted thermal shut down activation. Extreme over tightening of the mounting screws will cause severe physical stress resulting in cracked die and catastrophic IC failure. The recommended mounting screw size is M3 with a maximum torque of 50 N-cm. Additionally, it is best to use washers under the screws to distribute the force over a wider area or a screw with a wide flat head. To further distribute the mounting force a solid mounting bar in front of the package and secured in place with the two mounting screws may be used. Other mounting options include a spring clip. If the package is secured with pressure on the front of the package the maximum pressure on the molded plastic should not exceed 150N/mm<sup>2</sup>.

Additionally, if the mounting screws are used to force the package into correct alignment with the heat sink, package stress will be increased. This increase in package stress will result in reduced contact area with the heat sink increasing die operating temperature and possible catastrophic IC failure.

#### LAYOUT, GROUND LOOPS AND STABILITY

The LM4780 is designed to be stable when operated at a closed-loop gain of 10 or greater, but as with any other high-current amplifier, the LM4780 can be made to oscillate under certain conditions. These oscillations usually involve printed circuit board layout or output/input coupling issues.

When designing a layout, it is important to return the load ground, the output compensation ground, and the low level (feedback and input) grounds to the circuit board common ground point through separate paths. Otherwise, large currents flowing along a ground conductor will generate voltages on the conductor which can effectively act as signals at the input, resulting in high frequency oscillation or excessive distortion. It is advisable to keep the output compensation components and the  $0.1\mu$ F supply decoupling capacitors as close as possible to the LM4780 to reduce the effects of PCB trace resistance and inductance. For the same reason, the ground return paths should be as short as possible.

In general, with fast, high-current circuitry, all sorts of problems can arise from improper grounding which again can be avoided by returning all grounds separately to a common point. Without isolating the ground signals and returning the grounds to a common point, ground loops may occur.

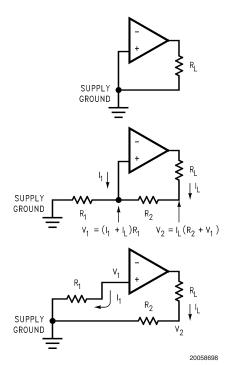

"Ground Loop" is the term used to describe situations occurring in ground systems where a difference in potential exists between two ground points. Ideally a ground is a ground, but unfortunately, in order for this to be true, ground conductors with zero resistance are necessary. Since real world ground leads possess finite resistance, currents running through them will cause finite voltage drops to exist. If two ground return lines tie into the same path at different points there will be a voltage drop between them. The first figure below shows a common ground example where the positive input ground and the load ground are returned to the supply ground point via the same wire. The addition of the finite wire resistance,  $R_2$ , results in a voltage difference between the two points as shown below.

The load current I<sub>L</sub> will be much larger than input bias current I<sub>1</sub>, thus V<sub>1</sub> will follow the output voltage directly, i.e. in phase. Therefore the voltage appearing at the non-inverting input is effectively positive feedback and the circuit may oscillate. If there was only one device to worry about then the values of R<sub>1</sub> and R<sub>2</sub> would probably be small enough to be ignored; however, several devices normally comprise a total system. Any ground return of a separate device, whose output is in phase, can feedback in a similar manner and cause instabilities. Out of phase ground loops also are troublesome, causing unexpected gain and phase errors.

The solution to most ground loop problems is to always use a single-point ground system, although this is sometimes impractical. The third figure above is an example of a singlepoint ground system.

The single-point ground concept should be applied rigorously to all components and all circuits when possible. Violations of single-point grounding are most common among printed circuit board designs, since the circuit is surrounded by large ground areas which invite the temptation to run a device to the closest ground spot. As a final rule, make all ground returns low resistance and low inductance by using large wire and wide traces.

Occasionally, current in the output leads (which function as antennas) can be coupled through the air to the amplifier input, resulting in high-frequency oscillation. This normally happens when the source impedance is high or the input leads are long. The problem can be eliminated by placing a small capacitor, C<sub>C</sub>, (on the order of 50pF to 500pF) across the LM4780 input terminals. Refer to the **External Components Description** section relating to component interaction with C<sub>f</sub>.

#### **REACTIVE LOADING**

It is hard for most power amplifiers to drive highly capacitive loads very effectively and normally results in oscillations or ringing on the square wave response. If the output of the LM4780 is connected directly to a capacitor with no series resistance, the square wave response will exhibit ringing if the capacitance is greater than about 0.2µF. If highly capacitive loads are expected due to long speaker cables, a method commonly employed to protect amplifiers from low impedances at high frequencies is to couple to the load through a  $10\Omega$  resistor in parallel with a  $0.7\mu$ H inductor. The inductor-resistor combination as shown in the Figure 5 isolates the feedback amplifier from the load by providing high output impedance at high frequencies thus allowing the  $10\Omega$ resistor to decouple the capacitive load and reduce the Q of the series resonant circuit. The LR combination also provides low output impedance at low frequencies thus shorting out the  $10\Omega$  resistor and allowing the amplifier to drive the series RC load (large capacitive load due to long speaker cables) directly.

#### INVERTING AMPLIFIER APPLICATION

The inverting amplifier configuration may be used instead of the more common non-inverting amplifier configuration shown in *Figure 1*. The inverting amplifier can have better THD+N performance and eliminates the need for a large capacitor (Ci) reducing cost and space requirements. The values show in *Figure 6* are only one example of an amplifier with a gain of 20V/V (Gain = -R<sub>f</sub>/R<sub>i</sub>). For different resistor values, the value of R<sub>B</sub> should be eqaul to the parallel combination of R<sub>f</sub> and Ri.

If the DC blocking input capacitor  $(C_{IN})$  is used as shown, the lower -3dB point is found using Equation (8) as discussed in the **Proper Selection of External Components** section.

FIGURE 6. Inverting Amplifier Application Circuit

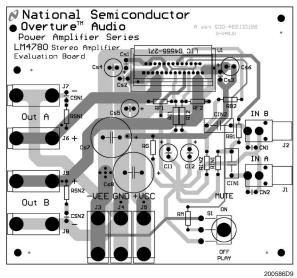

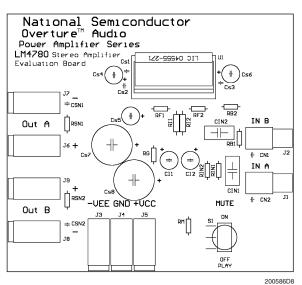

FIGURE 7. Reference PCB Schematic

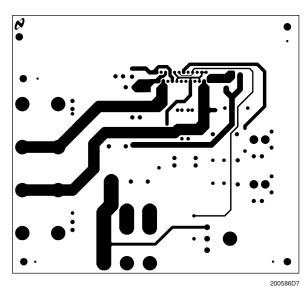

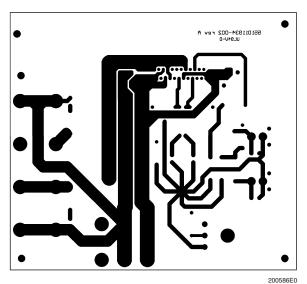

#### LM4780 REFERENCE BOARD ARTWORK

**Composite Layer**

Silk Layer

Top Layer

**Bottom Layer**

## Application Information (Continued) BILL OF MATERIALS FOR REFERENCE PCB

| Symbol                                                            | Value   | Tolerance | Type/Description            | Comment |

|-------------------------------------------------------------------|---------|-----------|-----------------------------|---------|

| R <sub>IN1</sub> , R <sub>IN2</sub>                               | 15kΩ    | 5%        | 1/4 Watt                    |         |

| R <sub>B1</sub> , R <sub>B2</sub>                                 | 1kΩ     | 1%        | 1/4 Watt                    |         |

| R <sub>F1</sub> , R <sub>F2</sub>                                 | 20kΩ    | 1%        | 1/4 Watt                    |         |

| R <sub>i1</sub> , R <sub>i2</sub>                                 | 1kΩ     | 1%        | 1/4 Watt                    |         |

| R <sub>SN1</sub> , R <sub>SN2</sub> ,                             | 2.7Ω    | 5%        | 1/4 Watt                    |         |

| R <sub>G</sub>                                                    | 2.7Ω    | 5%        | 1/4 Watt                    |         |

| R <sub>M</sub>                                                    | 10kΩ    | 5%        | 1/4 Watt                    |         |

| C <sub>IN1</sub> , C <sub>IN2</sub>                               | 1µF     | 10%       | Metallized Polyester Film   |         |

| C <sub>i1</sub> , C <sub>i2</sub> ,                               | 68µF    | 20%       | Electrolytic Radial / 50V   |         |

| C <sub>SN1</sub> , C <sub>SN2</sub>                               | 0.1µF   | 20%       | Monolithic Ceramic          |         |

| C <sub>N1</sub> , C <sub>N2</sub>                                 | 15pF    | 20%       | Monolithic Ceramic          |         |

| C <sub>S1</sub> , C <sub>S2</sub> , C <sub>S3</sub>               | 0.1µF   | 20%       | Monolithic Ceramic          |         |

| C <sub>S4</sub> , C <sub>S5</sub> , C <sub>S6</sub>               | 10µF    | 20%       | Electrolytic Radial / 50V   |         |

| C <sub>S7</sub> , C <sub>S8</sub>                                 | 1,000µF | 20%       | Electrolytic Radial / 50V   |         |

| S <sub>1</sub>                                                    |         |           | SPDT (on-on) Switch         |         |

| J <sub>1</sub> , J <sub>2</sub>                                   |         |           | Non-Switched PC Mount RCA   |         |

|                                                                   |         |           | Jack                        |         |

| J <sub>4</sub> , J <sub>7</sub> , J <sub>8</sub>                  |         |           | PCB Banana Jack - BLACK     |         |

| J <sub>3</sub> , J <sub>5</sub> , J <sub>6</sub> , J <sub>9</sub> |         |           | PCB Banana Jack - RED       |         |

| U <sub>1</sub>                                                    |         |           | 27 lead TO-220 Power Socket |         |

|                                                                   |         |           | with push lever release or  |         |

|                                                                   |         |           | LM4780 IC                   |         |

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.

# National Semiconductor was acquired by Texas Instruments.

http://www.ti.com/corp/docs/investor\_relations/pr\_09\_23\_2011\_national\_semiconductor.html

This file is the datasheet for the following electronic components:

LM4780 - http://www.ti.com/product/Im4780?HQS=TI-null-null-dscatalog-df-pf-null-wwe LM4780TA - http://www.ti.com/product/Im4780ta?HQS=TI-null-null-dscatalog-df-pf-null-wwe