Cache de memória e unidade de busca

Só para relembrar, o cache de memória é uma memória de alta velocidade (RAM estática ou SRAM) que está dentro do processador, usada para armazenar dados que o processador pode precisar. Se o dado requerido pelo processador não estiver localizado no cache, ele deve buscá-lo na lenta memória RAM, o que reduz o desempenho do micro, já que o processador acessa a memória RAM através do barramento local. Por exemplo, em um processador de 3,2 GHz, o cache de memória é acessado a 3,2 GHz enquanto que a memória RAM é acessada a apenas 800 MHz.

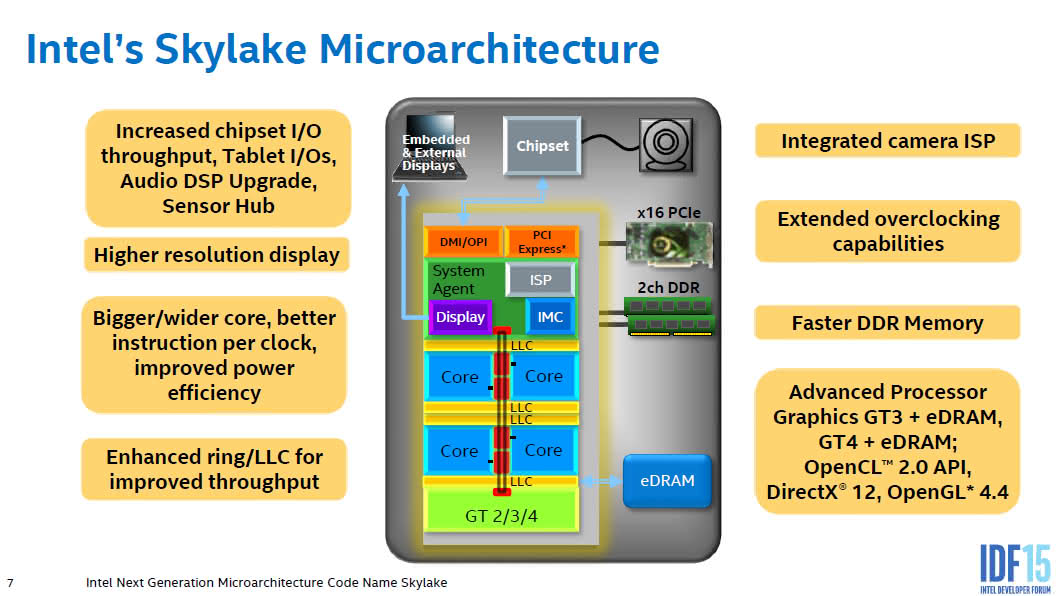

A arquitetura Core foi criada com o conceito da tecnologia de múltiplos núcleos em mente, ou seja, mais de um núcleo de processamento dentro de um único processador físico. O processador Pentium D é uma versão de dois núcleos do Pentium 4 e cada núcleo tem o seu próprio cache L2. O problema desta implementação é que em um dado momento o cache de memória L2 de um dos núcleos pode “acabar”, enquanto que o cache L2 do outro núcleo ainda tem partes não usadas. Quando isto acontece o primeiro núcleo precisa ir à lenta memória RAM, mesmo que haja espaço no cache L2 do segundo núcleo que poderia ser usado para armazenar dados e evitar que o primeiro núcleo acessasse a memória RAM.

Na arquitetura Core este problema foi resolvido. O cache de memória L2 é compartilhado, o que significa que ambos os núcleos podem usar a mesma memória cache L2, configurando dinamicamente a quantidade que cada núcleo usará. Em um processador com 2 MiB de cache L2, por exemplo, um núcleo pode estar usando 1,5 MiB enquanto que o outro pode estar usando 512 kiB (0,5 MiB), ao contrário do valor fixo 50%-50% usado pelos processadores de dois núcleos da arquitetura anterior.

E não é só isso. As pré-buscas são compartilhadas entre os núcleos, ou seja, se o controlador de cache carregar um bloco de dados para ser usado pelo primeiro núcleo, o segundo núcleo também pode usar o dado já carregado no cache. Na arquitetura anterior, se o segundo núcleo precisasse de um dado armazenado no cache L2 do primeiro núcleo, ele tinha que acessar o tal dado através do barramento externo (que trabalha com um clock muito menor do que o clock interno do processador) ou até mesmo pegar o dado requerido diretamente da lenta memória RAM.

A Intel também aprimorou a unidade de pré-busca do processador, que procura por padrões utilizados pelo processador na buscar dados na memória, com o objetivo de tentar “adivinhar” que dado o processador carregará, copiando-o antecipadamente para o cache de memória antes que o processador realmente precise dele. Por exemplo, se o processador acaba de carregar dados do endereço 1, e depois do endereço 3 e em seguida do endereço 5, a unidade de pré-busca do processador “chutará” que o programa em execução carregará dados do endereço 7, copiando os dados contidos neste endereço para o cache antes que o processador solicite. Na verdade, esta ideia não é nova e todos os processadores desde o Pentium Pro utilizam algum tipo de previsão para preencher o cache L2 com dados que o processador poderá precisar. Na arquitetura Core, a Intel simplesmente aprimorou este recurso fazendo com que a unidade de pré-busca procure por padrões nos dados solicitados em vez de simplesmente indicadores estáticos de qual dado o processador solicitará.

Respostas recomendadas

Crie uma conta ou entre para comentar

Você precisa ser um usuário para fazer um comentário

Criar uma conta

Crie uma nova conta em nossa comunidade. É fácil!

Crie uma nova contaEntrar

Já tem uma conta? Faça o login.

Entrar agora