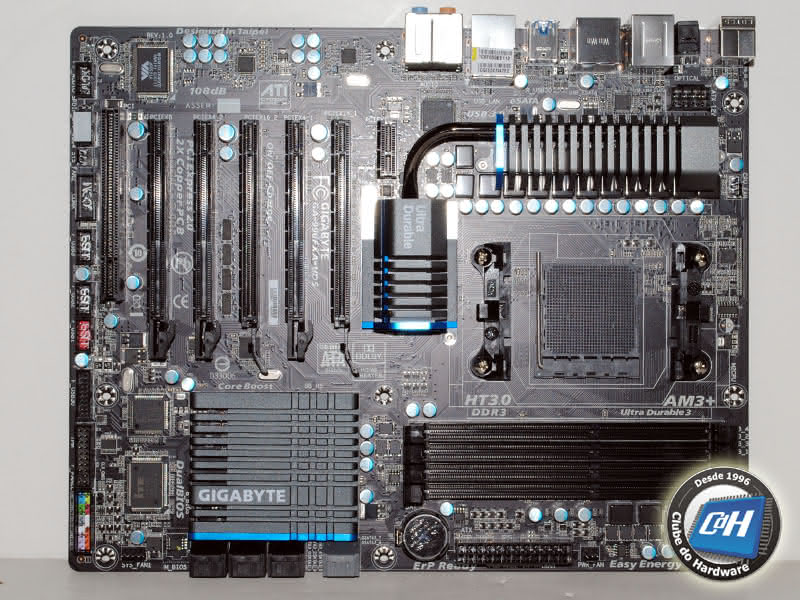

Regulador de Tensão

O circuito regulador de tensão do processador da 990FXA-UD5 tem oito fases para a tensão principal do processador (Vcore ou VDD) e duas fases para a tensão VDDNB do processador (controlador de memória integrado, barramento HyperTransport e cache de memória L3). Portanto esta placa-mãe tem uma configuração “8+2”.

Figura 8: Circuito regulador de tensão

Figura 9: Circuito regulador de tensão

Esta placa-mãe usa bobinas com núcleo de ferrite, que apresentam menor perda de energia do que as bobinas de ferro (ou seja, elas aumentam a eficiência) e capacitores sólidos. Cada fase é controlada por um circuito integrado SiC769CD, que combina os três transistores requeridos (“lado alto”, “lado baixo” e “driver”) em um único chip, além de permitir que o clock de chaveamento seja de 1 MHz, o que faz com que a eficiência seja maior do que 90% (normalmente os circuitos reguladores de tensão chaveiam a 250 kHz). Circuitos integrados com essas características são também conhecidos como “DrMOS”.

Se você quer aprender mais sobre o circuito regulador de tensão, leia o nosso tutorial sobre o assunto.

Respostas recomendadas