Introdução

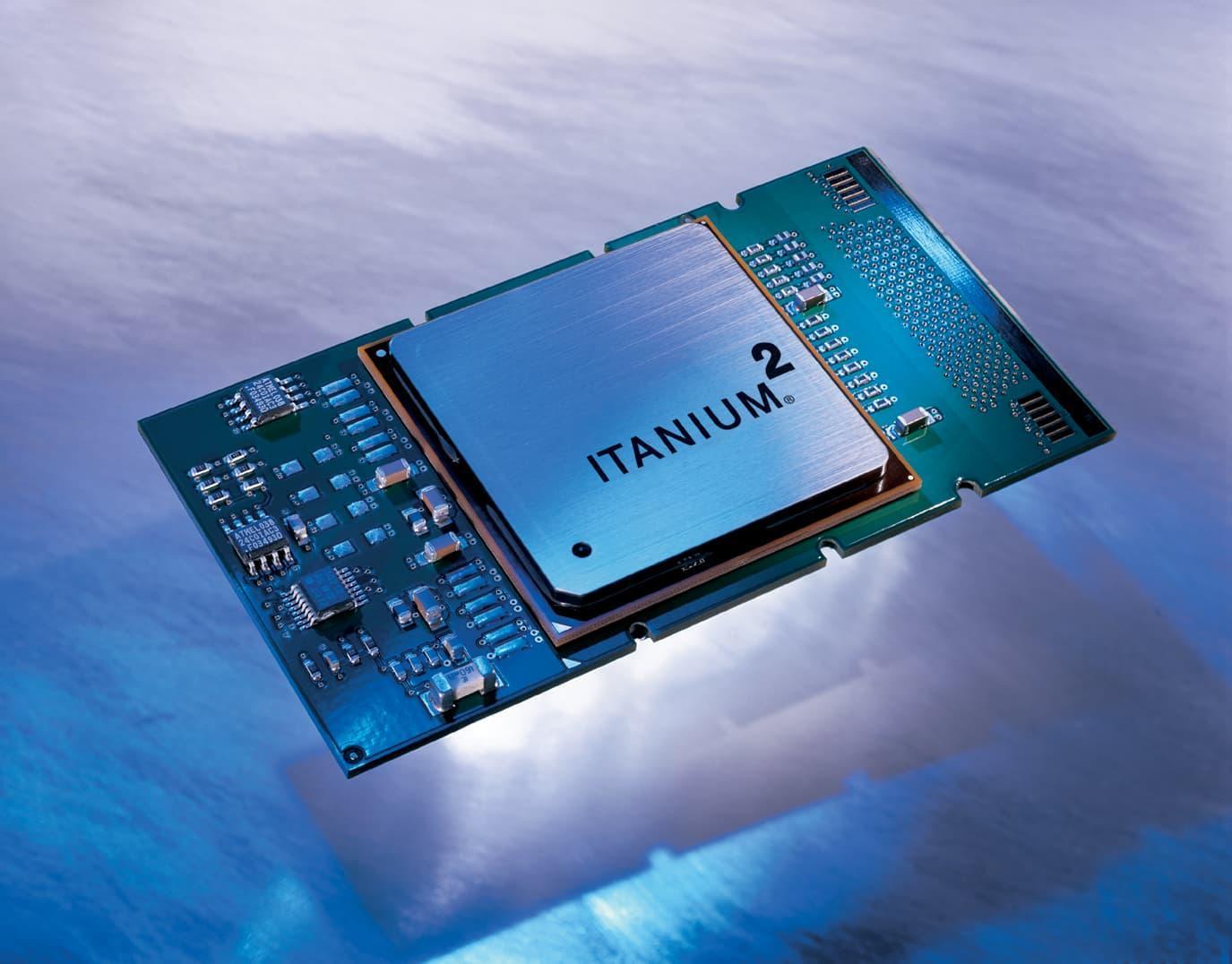

Desde 1994, Intel e HP vêm trabalhando numa proposta de 64 bits. Sua arquitetura deveria possibilitar aos processadores CISC um passo grande o suficiente para ultrapassar os processadores RISC. Usando a técnica denominada VLIW, ainda experimental na época, e criando o modelo EPIC, eles propuseram a arquitetura Merced, que ficou prometida para início do ano 2000. Como a conjuntura mudou, os processadores Pentium III e IV e o Athlon ofereceram desempenho excepcional, ultrapassando 1 GHz, e ainda devido ao preço elevado dessa nova arquitetura e a pouca disponibilidade de programas para 64 bits, o cronograma foi atrasado e o lançamento da arquitetura IA-64 deverá ocorrer somente neste ano.

A sigla VLIW significa “Palavra de Instrução Muito Grande”, do inglês “Very Large Instruction Word”. Processadores que usam essa técnica acessam a memória transferindo longas palavras de programa, sendo que, em cada palavra, estão empacotadas várias instruções. No caso da IA-64, são usadas três instruções para cada pacote de 128 bits. Como cada instrução tem 41 bits, sobram 5 bits que são usados para indicar os tipos de instruções que foram empacotadas. A Figura 1 apresenta o esquema de empacotamento das instruções. Esse empacotamento diminui a quantidade de acessos à memória, cabendo ao compilador a tarefa de agrupar as instruções de forma a tirar o melhor proveito da arquitetura.

Figura 1: Empacotamento das instruções usada na arquitetura IA-64.

Como já foi dito, o campo de 5 bits, rotulado como “Indicador”, serve para indicar os tipos de instruções empacotadas. Esses 5 bits oferecem 32 tipos de empacotamentos possíveis que, na verdade, são reduzidos para 24 tipos, já que 8 não são utilizados Cada instrução usa um dos recursos da CPU, que estão listados a seguir, e que podem ser identificados na Figura 2:

- Unidade I: números inteiros;

- Unidade F - operações a ponto-flutuante;

- Unidade M - acessos à memória; e

- Unidade B - tratamento de desvios.

A arquitetura que a Intel propõe para executar essas instruções, que foi denominada Itanium, é versátil e promete desempenho através da execução simultânea (paralela) de até 6 instruções. A Figura 2 apresenta o diagrama em blocos desta arquitetura que faz uso de um “pipeline” de 10 estágios.

Figura 2: Diagrama em blocos da CPU Itanium (arquitetura IA-64).

As arquiteturas IA-64 recebem a sigla EPIC, do inglês “Explicit Parallel Instruction Computing”, que é traduzida como “Computação com Paralelismo de Instruções Explícito”. Com essa sigla, a Intel quer dizer que o compilador será o grande responsável por determinar e explicitar o paralelismo presente nas instruções a serem executadas. Isto é uma combinação de conceitos chamados de especulação, predicação e paralelismo explícito. A seguir, estudaremos rapidamente cada um deles.

O Paralelismo a Nível de Instrução (IPL - “Instruction Level Parallelism”) é a habilidade de executar múltiplas instruções ao mesmo tempo. Como já vimos, a arquitetura IA-64 permite empacotar instruções independentes para serem executadas em paralelo e, por cada período de relógio, é capaz de tratar múltiplos pacotes. Devido ao grande número de recursos em paralelo, tais como grande quantidade de registradores e múltiplas unidades de execução, é possível ao compilador gerenciar e programar a computação em paralelo. Os compiladores usados para as arquiteturas tradicionais são limitados em sua capacidade especulativa porque nem sempre há como ter certeza se a especulação será corretamente gerenciada pelo processador. A arquitetura IA-64 permite ao compilador explorar a informação especulativa sem sacrificar a correta execução de uma aplicação.

A arquitetura IA-64 tem mecanismos denominados indicador de instruções, sugestões para desvios e cache, que permitem ao compilador enviar ao processador informações obtidas durante o tempo de compilação. Essas informações minimizam as penalidades advindas dos desvios e ausências de cache (“cache misses”).

Existem dois tipos de especulação: a de dados e a de controle. Com a especulação, o compilador antecipa uma operação de forma que sua latência (tempo gasto) seja retirada do caminho crítico. A especulação é uma forma de permitir ao compilador evitar que operações lentas atrapalhem o paralelismo das instruções. A especulação de controle é a execução de uma operação antes do desvio que a precede. Por sua vez, a especulação de dados é a execução de uma carga da memória (“load”) antes de uma operação de armazenagem (“store”) que a precede e com a qual pode estar relacionada.

Com a “predicação”, do inglês “predication”, marca-se com predicados todos os ramos dos desvios condicionais que, em seguida, são despachados para a execução em paralelo, porém, executa-se apenas os que forem necessários. Assim, é possível preparar a execução das instruções antes mesmo de se ter resolvido o desvio condicional. Além da remoção de desvios através do uso de predicados, na arquitetura IA-64, existe ainda uma série de mecanismos que devem diminuir o erro na predição dos desvios e o custo quando este erro acontece.

A arquitetura IA-64 traz uma grande quantidade de registradores. São 128 registradores gerais (inteiros), 128 registradores de ponto-flutuante, 64 registradores de 1 bit, para os predicados, e diversos outros registradores para configuração, gerenciamento e monitoração do desempenho da CPU.

Para finalizar, vemos que a Intel promete compatibilidade com os aplicativos de 32 bits (IA-32). Eles deverão rodar sem qualquer alteração desde que o sistema operacional e o “firmware” tenham recursos para isso. Deverá ser possível rodar aplicativos no modo real (16 bits), modo protegido (32 bits) e modo virtual 86 (16 bits). Com isso, eles querem dizer que a CPU poderá operar no modo IA-64 ou modo IA-32. Existem instruções especiais para transitar de um modo para outro, como mostrado na Figura 3.

Figura 3: Modelo de transição dos conjuntos de instruções.

As três instruções que fazem a transição entre os conjunto de instruções são:

- JMPE (IA-32): salta para um instrução de 64 bits e muda para o modo IA-64;

- br.ia (IA-64): desvia para uma instrução de 32 bits e muda para o modo IA-32;

- Interrupções transicionam para o modo IA-64, permitindo assim o atendimento de todas as condições de interrupção e

- rfi (IA-64): é o retorno de interrupção; o retorno se dá tanto para uma situação IA-32 quanto para uma IA-64, dependendo da situação presente no momento em que a interrupção for invocada.

Respostas recomendadas

Não há comentários para mostrar.

Crie uma conta ou entre para comentar

Você precisa ser um usuário para fazer um comentário

Criar uma conta

Crie uma nova conta em nossa comunidade. É fácil!

Crie uma nova contaEntrar

Já tem uma conta? Faça o login.

Entrar agora