Na semana passada, fomos a San Francisco, nos EUA, a convite da AMD, para um evento chamado "Next Horizon". Uma das novidades apresentadas foi o lançamento dos processadores EPYC de segunda geração, baseados na arquitetura Zen 2 e processo de fabricação de 7 nm.

Os processadores EPYC são voltados a datacenters, ou seja, não são processadores para computadores domésticos, porém utilizam a mesma arquitetura básica x86-64 encontrada nos computadores de mesa "comuns". Na verdade, os processadores EPYC de primeira geração, lançados em 2017, utilizam a mesma arquitetura de núcleos Zen utilizada nos processadores Ryzen 3, Ryzen 5, Ryzen 7 e Ryzen Threadripper.

O codinome destes novos processadores EPYC de segunda geração é "Rome", e eles são baseados na nova arquitetura "Zen 2".

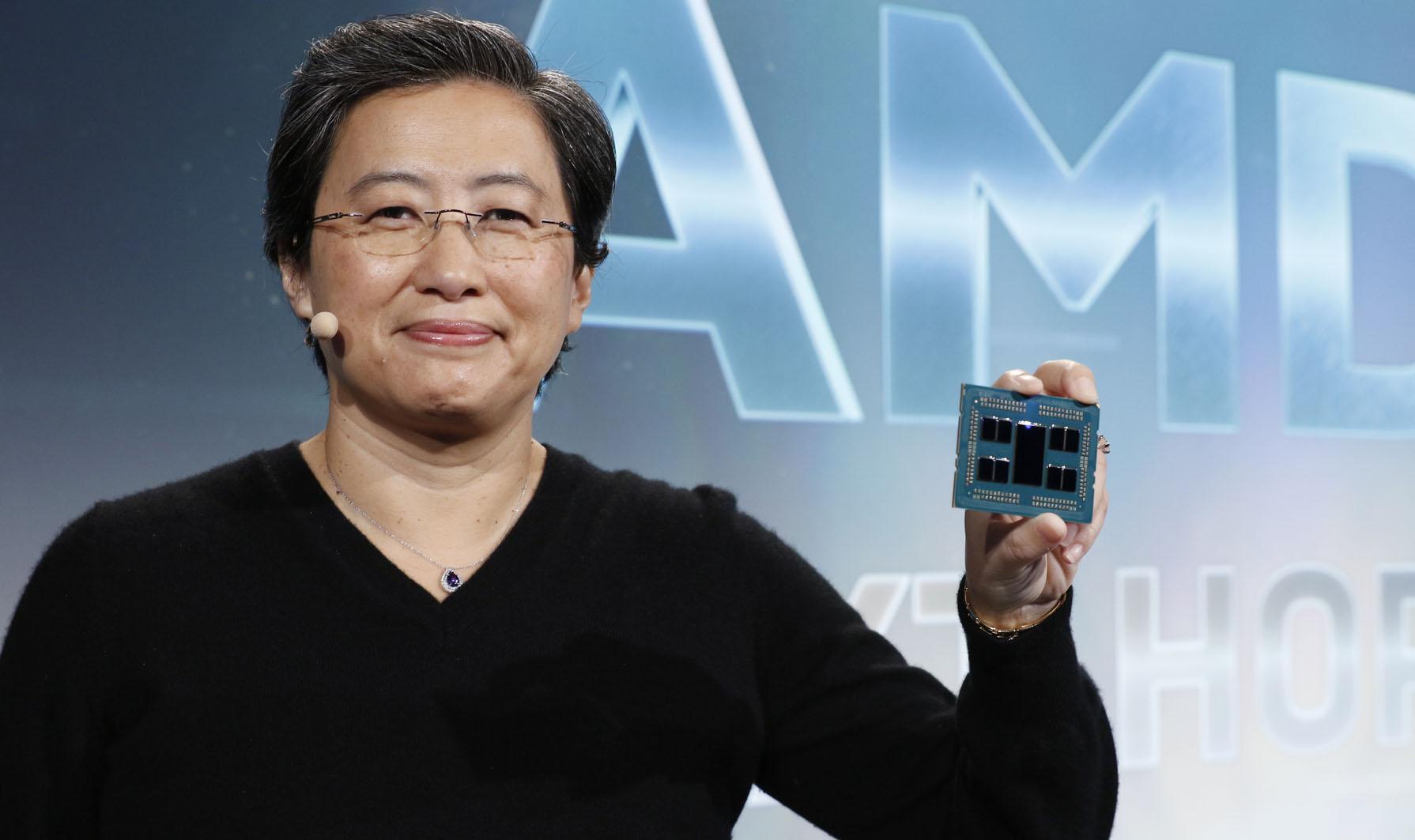

O evento começou com uma apresentação feita pela presidente da AMD, Lisa Su, que enfatizou o uso destes processadores em simulações de larga escala, previsão do tempo, estudos sobre energia e biologia computacional, análise de "big data", inteligência artificial e demais aplicações que demandam alto desempenho de processamento em nuvem.

Figura 1: apresentação da nova linha de proessadores

Foi apresentada a nova parceria da AMD com a AWS (o serviço de nuvem da Amazon), que passa a utilizar servidores baseados em processadores EPYC.

A seguir, acompanhamos a fala de Mark Papermaster, CTO (Chief Technology Officer) de tecnologia e engenharia da AMD. Ele apresentou o roadmap dos núcleos de processadores da AMD, com o arquitetura "Zen" utilizada pelos processadores Ryzen e EPYC de primeira geração, fabricada em 14 nm, a arquitetura "Zen+", de 12 nm, utilizada pelos processadores Ryzen de segunda geração (como este, por exemplo), e a agora anunciada arquitetura "Zen 2", fabricada em 7 nm, e que será utilizada primeiramente pelos processadores EPYC de segunda geração. Também foi anunciada a arquitetura "Zen 3", com lançamento previsto para 2020.

Figura 2: roadmap

Segundo a AMD, estes núcleos fabricados em 7 nm têm uma densidade de transistores duas vezes maior do que a da geração anterior, possibilita um consumo energético 50% menor mantendo o mesmo desempenho ou um desempenho pelo menos 25% superior mantendo o mesmo consumo.

Além da tecnologia de fabricação em 7 nm, a geração Zen 2 recebeu uma otimização no pipeline de execução, no circuito de previsão de desvios, no cache de instruções e na unidade de ponto flutuante, que passa a ter 256 bits, em vez de 128 bits como na geração anterior. Todos estes avanços permitem, de acordo com a AMD, um grande aumento no desempenho por núcleo, em relação à arquitetura anterior.

Figura 3: previsão de consumo e desempenho

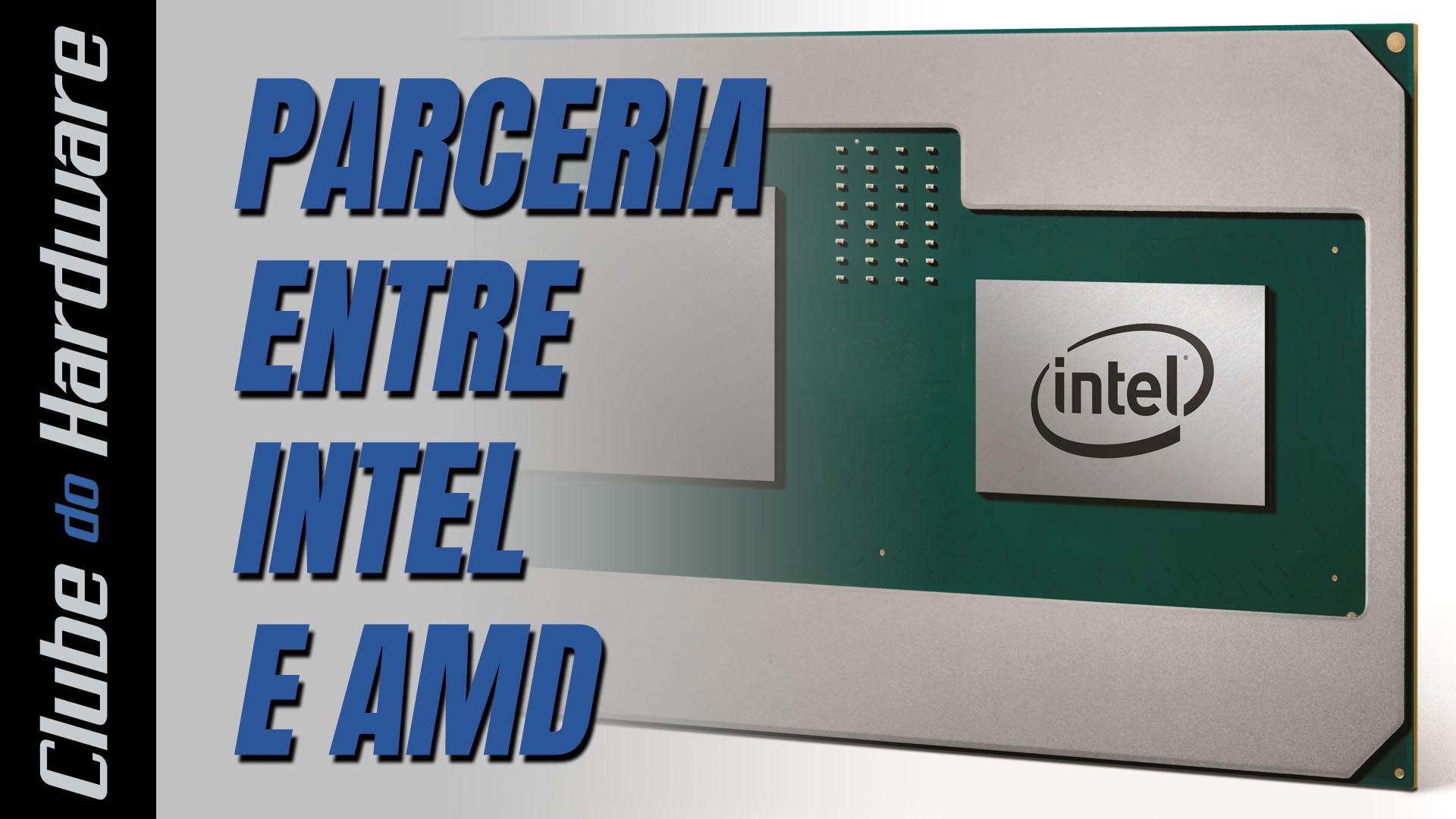

Os processadores EPYC da geração "Rome" utilizam uma estrutura modular, onde os núcleos de processamento e circuitos de entrada e saída são feitos em pastilhas de silício independentes (chamadas pela AMD de "chiplets"), interligadas entre si pelo barramento Infinity Fabric.

Figura 4: Lisa Su apresentando o EPYC Rome

Com este desenho modular, os processadores EPYC Rome podem ter até 64 núcleos físicos e 128 threads. Neste modelo, o encapsulamento do processador tem oito chips com os núcleos de processamento, fabricados em 7 nm, e e posicionados sobre um substrato contendo um chip de entrada e saída (I/O), que tem em seu interior os controladores de memória, PCI Express, etc. Este chip de entrada e saída é fabricado em 14 nm, segundo a AMD por ser uma tecnologia mais madura.

Cada chip (ou "die") com núcleos de processamento inclui dois CCX ("Core Complex"), e cada CCX possui quatro núcleos. Esta estrutura é semelhante à utilizada em todos os processadores Ryzen até agora, o que nos permite supor que em breve estes núcleos "Zen 2" de 7 nm estarão presentes nos processadores Ryzen de terceira geração voltados a usuários domésticos. A AMD ainda mantém em sigilo, porém, mais detalhes sobre os novos CCX, como a quantidade de cache, por exemplo.

Os processadores oferecem suporte a memória DDR4 em oito canais, com correção de erros (ECC).

Outra novidade é o uso de conexão PCI Express 4.0: os novos processadores EPYC Rome são os primeiros anunciados a utilizar esta tecnologia, que duplica a largura de banda disponível no atual padrão PCI Express 3.0. Estes processadores oferecem 128 pistas PCI Express 4.0.

Figura 5: apresentação da estrutura modular do processador

Também foi informado que os novos processadores EPYC da família "Rome" utilizam o mesmo soquete e são compatíveis com as placas-mãe para os modelos "Naples" de primeira geração. Além disso, foi prometido que a próxima geração, "Milan", baseada na arquitetura Zen 3, também será compatível com as placas-mãe atuais.

Obviamente, alguns recursos como conexão PCI Express 4.0 só estarão disponíveis quando forem utilizadas placas-mãe mais modernas.

A ideia geral que foi passada é que, graças ao processo de fabricação de 7 nm, foi possível fabricar um processador com 64 núcleos, o que permite que um computador com apenas um soquete tenha 128 threads. A ideia da AMD é, portanto, oferecer servidores com um único processador com desempenho semelhante aos modelos concorrentes (da Intel) que utilizam dois processadores, reduzindo assim o custo para datacenters.

Figura 6: Lisa Su finalizando a apresentação

Depois foi apresentada uma demonstração onde um computador utilizando um processador EPYC "Rome" com 64 núcleos renderizava uma imagem, sendo, segundo a AMD, mais rápido do que um sistema com dois processadores Intel Xeon 8180M (com 28 núcleos cada).

Pudemos fotografar uma dessas máquinas onde os protótipos estão instalados, mas, infelizmente, não pudemos vê-los em mais detalhes.

Figura 7: protótipo utilizando o EPYC de 64 núcleos

Na Figura 8, vemos uma ilustração dos módulos que compõe o processador EPYC com 64 núcleos. O chip grande ao centro têm os circuitos de entrada e saída do processador e é fabricado em 14 nm, enquanto cada um dois oito chips menores ("chiplets") contêm oito núcleos de processamento e é fabricado em 7 nm.

Figura 8: estrutura modular do processador EPYC "Rome" de 64 núcleos

-

8

8

-

1

1

Respostas recomendadas

Crie uma conta ou entre para comentar

Você precisa ser um usuário para fazer um comentário

Criar uma conta

Crie uma nova conta em nossa comunidade. É fácil!

Crie uma nova contaEntrar

Já tem uma conta? Faça o login.

Entrar agora