CISC versus RISC versus VLIW

Conta a história que as máquinas RISC ("Reduced Instruction Set Computer") surgiram quando os projetistas substituíram as instruções complexas por um conjuntos mais simples, mais veloz e de controle mais fácil. Com isso, o chip ficou menos sobrecarregado, sobrando mais área para ser usada em outras unidades funcionais.

A história real é um pouco diferente! As máquinas RISC nasceram da necessidade de simplificar-se a CPU. A ideia foi trocar complexidade da CPU por otimização durante a compilação. Usou-se então um conjunto de instruções pequeno mas veloz, que pudesse ser executado em paralelo e ainda que fosse de fácil controle. Um grande conjunto de registradores substituiu os complexos modos de endereçamento. Com a simplificação da unidade de controle, uma maior área do CI pode ser empenhada diretamente no processamento. O trabalho de arrumar as instruções, de forma a espremer o máximo desempenho da CPU, foi transferido para o compilador. Em outras palavras, boa parte da complexidade da CPU foi transferida para o compilador. Assim o termo RISC não é muito feliz pois ele faz referência apenas ao conjunto de instruções e ignora o importante papel do compilador em gerar programas otimizados para essas máquinas.

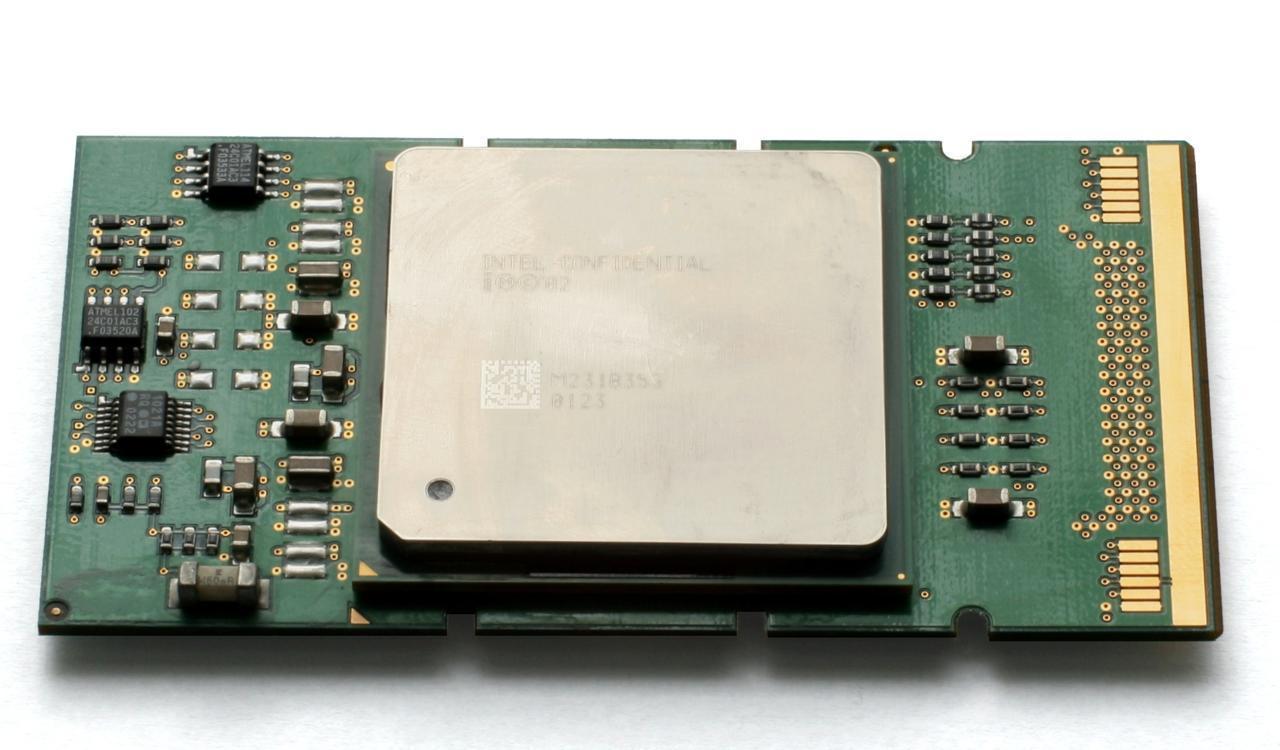

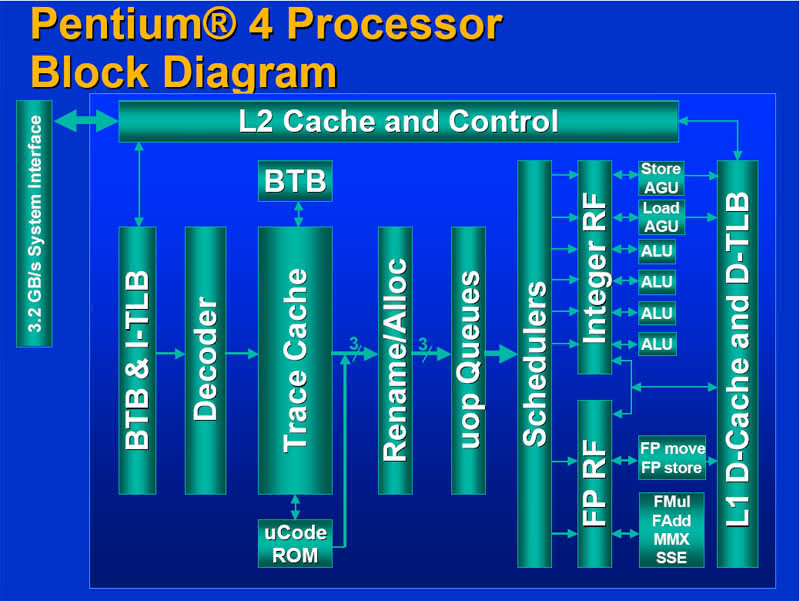

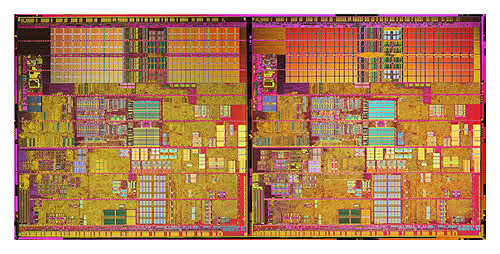

A família x86 começou com a CPU 8086, que é uma máquina CISC. Com a demanda por desempenho, os projetistas da Intel espremeram todo o desempenho passível de ser obtida com essa arquitetura. A evolução natural seria para uma arquitetura RISC, mas isso comprometeria seriamente a compatibilidade com o passado. A solução encontrada foi a de projetar uma máquina híbrida: uma casca CISC com um coração RISC. Assim são os Pentium Pro e Pentium II que traduzem as complexas instruções x86 em uma ou mais micro-operações que são executadas por uma máquina RISC. Essa micro-operações são de mais fácil controle e podem ser executadas em paralelo. Porém uma grande parte da CPU ainda é dedicada ao controle dessas instruções, à predição dos desvios e à tradução. As atuais CPUs possuem milhões de transistores, mas, desse total, apenas uma pequena parte é usada diretamente no processamento, pois a grande maioria é consumida no controle das instruções para possibilitar a execução fora de ordem e na predição dos desvios, ou seja, as atuais arquiteturas RISC/CISC estão complexas novamente e, por isso, é hora de aplicar o método: vamos simplificar a CPU e passar o trabalho de otimização para o compilador. Essa é a grande máxima da arquitetura IA-64, empregada no desenvolvimento da CPU Merced.

(1)(1)(1)_11zon_2_11zon.thumb.jpg.a0e335c490f32bc63b9d36e6e04c6f22.jpg)

Respostas recomendadas

Não há comentários para mostrar.

Crie uma conta ou entre para comentar

Você precisa ser um usuário para fazer um comentário

Criar uma conta

Crie uma nova conta em nossa comunidade. É fácil!

Crie uma nova contaEntrar

Já tem uma conta? Faça o login.

Entrar agora