Pipeline do Pentium 4

Pipeline é uma lista de todos os estágios que uma dada instrução precisa percorrer dentro do processador para ser executada. Nos processadores Intel de sexta geração, como o Pentium III, o pipeline tinha 11 estágios. O pipeline do Pentium 4 possui 20 estágios. Por isso, no Pentium 4 uma dada instrução demora mais para ser executada do que no processador Pentium III, por exemplo! Para você ter uma ideia, a situação é ainda pior nos novos processadores Pentium 4 com núcleo Prescott, já que os mesmos possuem um pipeline com 31 estágios! Impressionante!

Este aumento no número de estágios do pipeline foi criado para que os processadores rodassem com clocks mais elevados. Com mais estágios, cada um deles pode ser construído com poucos transistores o que facilita a obtenção de clocks maiores. Na verdade, o Pentium 4 é mais rápido do que o Pentium III apenas porque ele trabalha com um clock maior. Se eles operassem com o mesmo clock um Pentium III seria mais rápido do que um Pentium 4 por causa do tamanho do pipeline.

Por esse motivo, a Intel já anunciou que a oitava geração de seus processadores será baseada na arquitetura do Pentium M, que por sua vez é baseada na arquitetura da Intel de sexta geração (arquitetura do Pentium III) e não na arquitetura Netburst do Pentium 4.

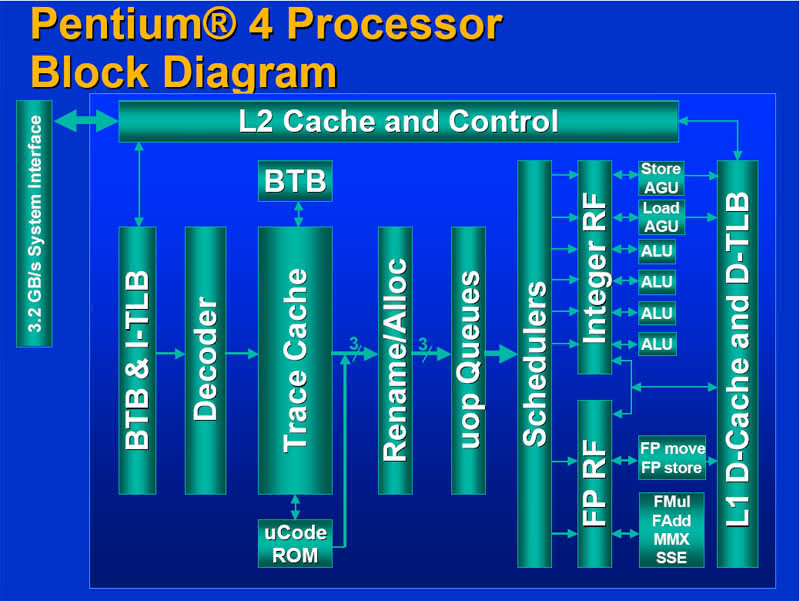

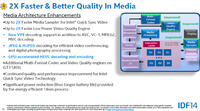

Na Figura 2 você pode ver os 20 estágios do pipeline do Pentium 4. Até agora a Intel não divulgou quais são os 31 estágios do pipeline dos processadores Pentium 4 baseados no núcleo Prescott, e por isso não podemos falar nada a respeito desta geração de Pentium 4.

Figura 2: Pipeline do Pentium 4.

Aqui está uma explicação básica de cada um dos estágios, que explica como uma dada instrução é processada por um processador Pentium 4. Se você acha isso complicado, não se preocupe. Isto é apenas um resumo do que falaremos nas próximas páginas.

- Ponteiro da próxima instrução do cache de microinstruções (TC Nxt IP, Trace cache next instruction pointer): Este estágio vê no buffer de destino de desvio (BTB) qual é a próxima microinstrução a ser executada. Esta etapa demora 2 estágios.

- Busca da próxima microinstrução no cache de microinstruções (TC Fetch, Trace cache fetch): Carrega, do cache de microinstrução, essa microinstrução. Esta etapa demora 2 estágios.

- Drive: Envia a microinstrução a ser executada à unidade de alocação de recursos e de renomeamento de registradores.

- Alocação de recursos (Alloc): Verifica quais recursos serão alocados pela microinstrução, como, por exemplo, o buffer de carga (load) ou o buffer de armazenamento (store).

- Renomeamento de Registradores (Rename): Renomeia os oito registradores padrão x86 em um dos 128 registradores internos presentes no Pentium 4. Esta etapa demora 2 estágios.

- Fila (Queue): As microinstruções são armazenadas em filas de acordo com o seu tipo (por exemplo, inteiro ou ponto flutuante). Elas são mantidas na fila até haver espaço no agendador de execução correspondente ao tipo de instrução a ser executada.

- Agendamento (Sch, Schedule): As microinstruções são agendadas de acordo com o seu tipo (inteiro, ponto flutuante, etc). Antes de chegar nesta etapa, as microinstruções são entregues em ordem, ou seja, na mesma ordem em que apareciam no programa. Nesta etapa, o agendador reordena as instruções de forma que estas sejam executadas da melhor forma possível, isto é, que não fique nenhuma unidade de execução vazia. Por exemplo, se uma unidade de ponto flutuante vai ficar disponível, o agendador procurará por uma instrução de ponto flutuante para mandá-la para esta unidade, mesmo que a próxima instrução no programa seja uma instrução que opere com números inteiros. Os agendadores são o coração da execução fora de ordem dos processadores de 7ª geração. Esta etapa demora três estágios.

- Envio (Disp, Dispatch): As microinstruções são enviadas às unidades de execução adequadas. Esta etapa é dividida em dois estágios.

- Leitura dos registradores internos (RF): Os registradores internos, armazenados no pool de instruções, são lidos. Esta etapa demora dois estágios.

- Execução (Ex): As microinstruções são executadas.

- Flags (Flgs): Atualiza os flags do processador.

- Verificação de desvios (Br Ck, Branch check): Verifica se o desvio tomado pelo programa é o mesmo que o previsto pelo circuito de previsão de desvio.

- Drive: Envia o resultado dessa verificação para o buffer de destino de desvio (BTB) localizado na entrada do processador.

Respostas recomendadas

Não há comentários para mostrar.

Crie uma conta ou entre para comentar

Você precisa ser um usuário para fazer um comentário

Criar uma conta

Crie uma nova conta em nossa comunidade. É fácil!

Crie uma nova contaEntrar

Já tem uma conta? Faça o login.

Entrar agora