Decodificador de instruções: fusão de instruções

Um novo conceito foi introduzido com a arquitetura Core: fusão de instruções (macro-fusion). Fusão de instruções é a capacidade de combinar duas instruções x86 dentro de apenas uma microinstrução. Isto aumenta o desempenho e diminui o consumo do processador, já que ele executará apenas uma microinstrução em vez de duas.

Este esquema, no entanto, é limitado a instruções de desvio condicional e de comparação (ou seja, instruções CMP, TEST e Jcc). Por exemplo, considere o trecho do programa abaixo:

… load eax, [mem1] cmp eax, [mem2] jne destino …

O que isto faz é carregar para o registrador de 32 bits EAX dados contidos na posição de memória 1, compara seus valores com os dados contidos na posição de memória 2 e, se eles forem diferentes (jne = vá para se não for igual), o programa vai para o endereço “destino”, mas se eles forem iguais, o programa continua na posição atual.

Com a fusão de instruções as instruções de comparação (cmp) e condicional (jne) serão concatenadas dentro de uma única microinstrução. Então, depois de passar pelo decodificador de instrução, esta parte do programa será algo como:

… load eax, [mem1] cmp eax, [mem2] + jne destino …

Como você pode ver, economizamos uma microinstrução. Quanto menor o número de instruções a serem executadas, mais rápido o computador realizará a execução da tarefa além de consumir menos.

O decodificador de instruções foi ampliado na arquitetura Core, com a adição de mais um decodificador de instruções simples, para um total de quatro decodificadores, enquanto que os processadores Pentium M e anteriores baseados da microarquitetura P6 e processadores baseados na microarquitetura Netburst, como o Pentium 4, podem decodificar apenas três.

Por causa da fusão de instruções o decodificador de instruções da arquitetura Core pega cinco instruções por vez da fila de instruções, apesar de ele poder decodificar apenas quatro instruções por pulso de clock. Isto é feito assim porque se duas das cinco instruções forem fundidas em apenas uma, o decodificador pode ainda decodificar quatro instruções por pulso de clock. De outro modo ele ficaria parcialmente ocioso toda vez que uma fusão de instruções aparecesse, ou seja, ele entregaria apenas três microinstruções em sua saída enquanto que ele é capaz de entregar até quatro.

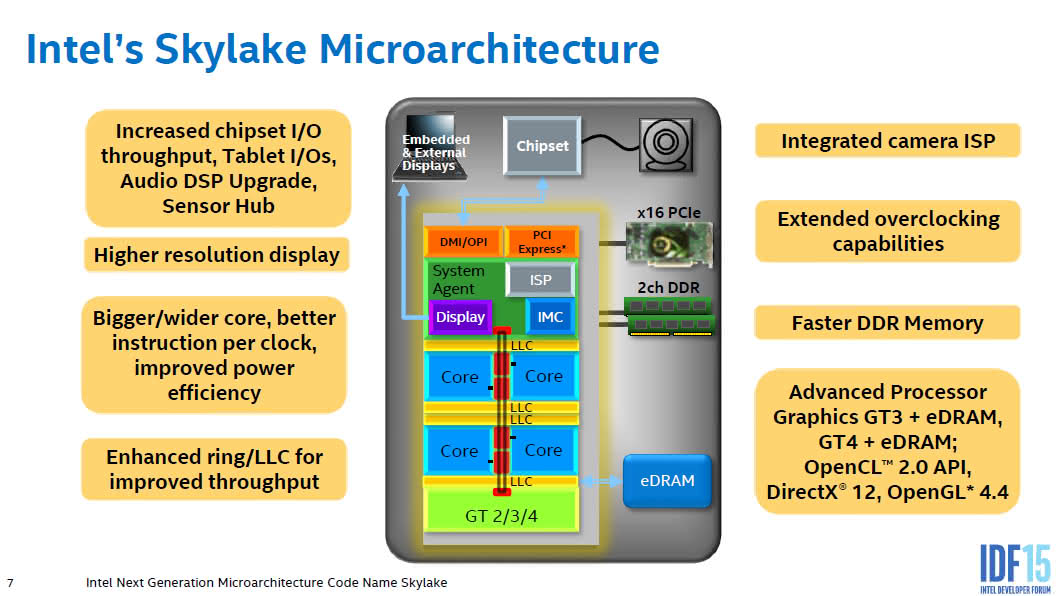

Na Figura 1 você pode ver um breve resumo do que explicamos nesta página e nas anteriores.

Figura 1: Unidade de busca e decodificador de instruções da arquitetura Core.

Respostas recomendadas

Crie uma conta ou entre para comentar

Você precisa ser um usuário para fazer um comentário

Criar uma conta

Crie uma nova conta em nossa comunidade. É fácil!

Crie uma nova contaEntrar

Já tem uma conta? Faça o login.

Entrar agora