MZ Editora

Membro VIP-

Posts

28 -

Cadastrado em

-

Última visita

Nunca

Tipo de conteúdo

Artigos

Selos

Fabricantes

Livros

Cursos

Análises

Fórum

Tudo que MZ Editora postou

-

Tópico para a discussão do seguinte conteúdo publicado no Clube do Hardware: PCI Plug and Play "Aprenda sobre o funcionamento do barramento PCI Plug and Play." Comentários são bem-vindos. Atenciosamente, Equipe Clube do Hardware https://www.clubedohardware.com.br

-

Processadores Para o Próximo Milênio - Parte 4

MZ Editora postou um tópico em Comentários de artigos

Tópico para a discussão do seguinte conteúdo publicado no Clube do Hardware: Processadores Para o Próximo Milênio - Parte 4 "Nesta parte final da série "Processadores para o próximo milênio", falamos sobre supercomputadores." Comentários são bem-vindos. Atenciosamente, Equipe Clube do Hardware https://www.clubedohardware.com.br -

Processadores Para o Próximo Milênio - Parte 3

MZ Editora postou um tópico em Comentários de artigos

Tópico para a discussão do seguinte conteúdo publicado no Clube do Hardware: Processadores Para o Próximo Milênio - Parte 3 "Na terceira parte desta série de artigos mostramos alguns exemplos de arquiteturas paralelas propostas pela IBM." Comentários são bem-vindos. Atenciosamente, Equipe Clube do Hardware https://www.clubedohardware.com.br -

Processadores Para o Próximo Milênio - Parte 2

MZ Editora postou um tópico em Comentários de artigos

Tópico para a discussão do seguinte conteúdo publicado no Clube do Hardware: Processadores Para o Próximo Milênio - Parte 2 "Série que discute os avanços na arquitetura de processadores. Nesta parte, discutimos o conceito de paralelismo." Comentários são bem-vindos. Atenciosamente, Equipe Clube do Hardware https://www.clubedohardware.com.br -

Tópico para a discussão do seguinte conteúdo publicado no Clube do Hardware: Arquitetura de 64 bits da AMD (x86-64) "Aprenda tudo sobre o funcionamento da arquitetura de 64bits da AMD." Comentários são bem-vindos. Atenciosamente, Equipe Clube do Hardware https://www.clubedohardware.com.br

-

Tópico para a discussão do seguinte conteúdo publicado no Clube do Hardware: Arquitetura de 64 bits da Intel (IA-64) "Aprenda tudo sobre o funcionamento da arquitetura IA-64 da Intel, utilizada pelos processadores Itanium." Comentários são bem-vindos. Atenciosamente, Equipe Clube do Hardware https://www.clubedohardware.com.br

-

Tópico para a discussão do seguinte conteúdo publicado no Clube do Hardware: ISA Plug and Play "Aprenda sobre o funcionamento do barramento ISA Plug and Play." Comentários são bem-vindos. Atenciosamente, Equipe Clube do Hardware https://www.clubedohardware.com.br

-

Tópico para a discussão do seguinte conteúdo publicado no Clube do Hardware: Arquitetura Plug and Play "Aprenda sobre o funcionamento da Arquitetura Plug and Play." Comentários são bem-vindos. Atenciosamente, Equipe Clube do Hardware https://www.clubedohardware.com.br

-

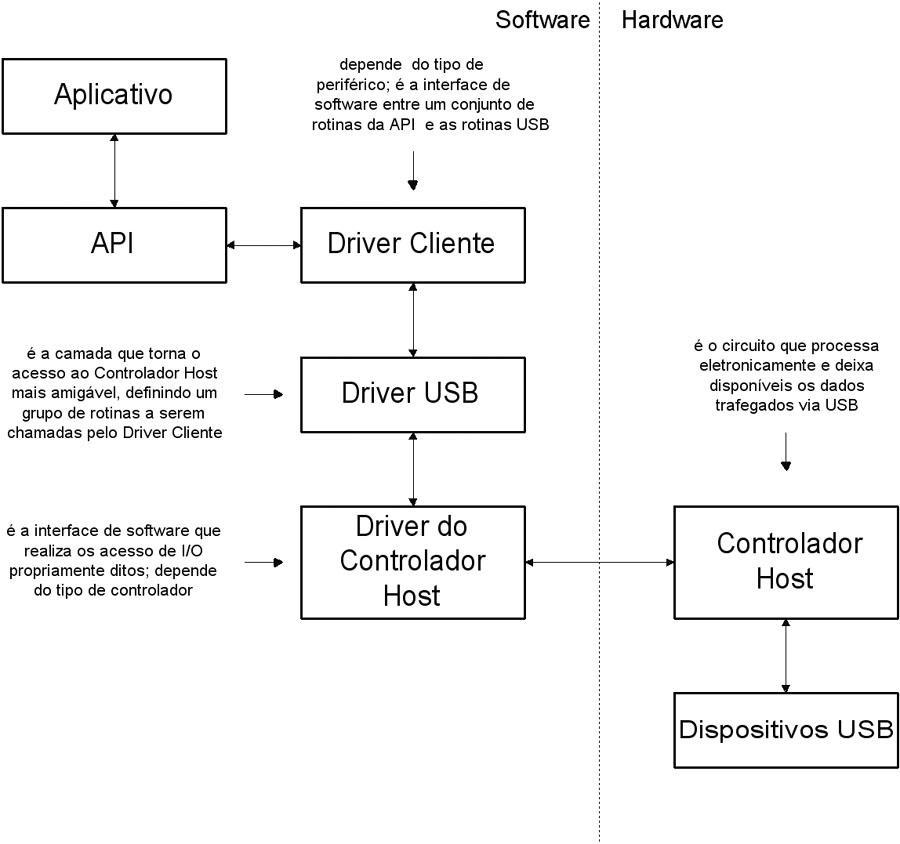

Tópico para a discussão do seguinte conteúdo publicado no Clube do Hardware: USB - Estrutura de Software "Saiba tudo sobre a estrutura de software do barramento USB." Comentários são bem-vindos. Atenciosamente, Equipe Clube do Hardware https://www.clubedohardware.com.br

-

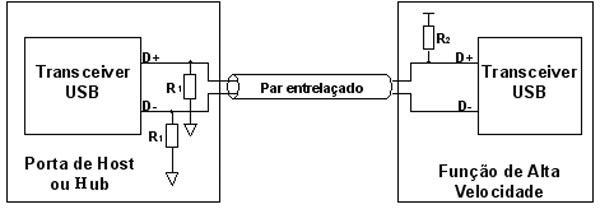

Tópico para a discussão do seguinte conteúdo publicado no Clube do Hardware: USB - Estrutura Elétrica "Saiba tudo sobre a estrutura elétrica do barramento USB." Comentários são bem-vindos. Atenciosamente, Equipe Clube do Hardware https://www.clubedohardware.com.br

-

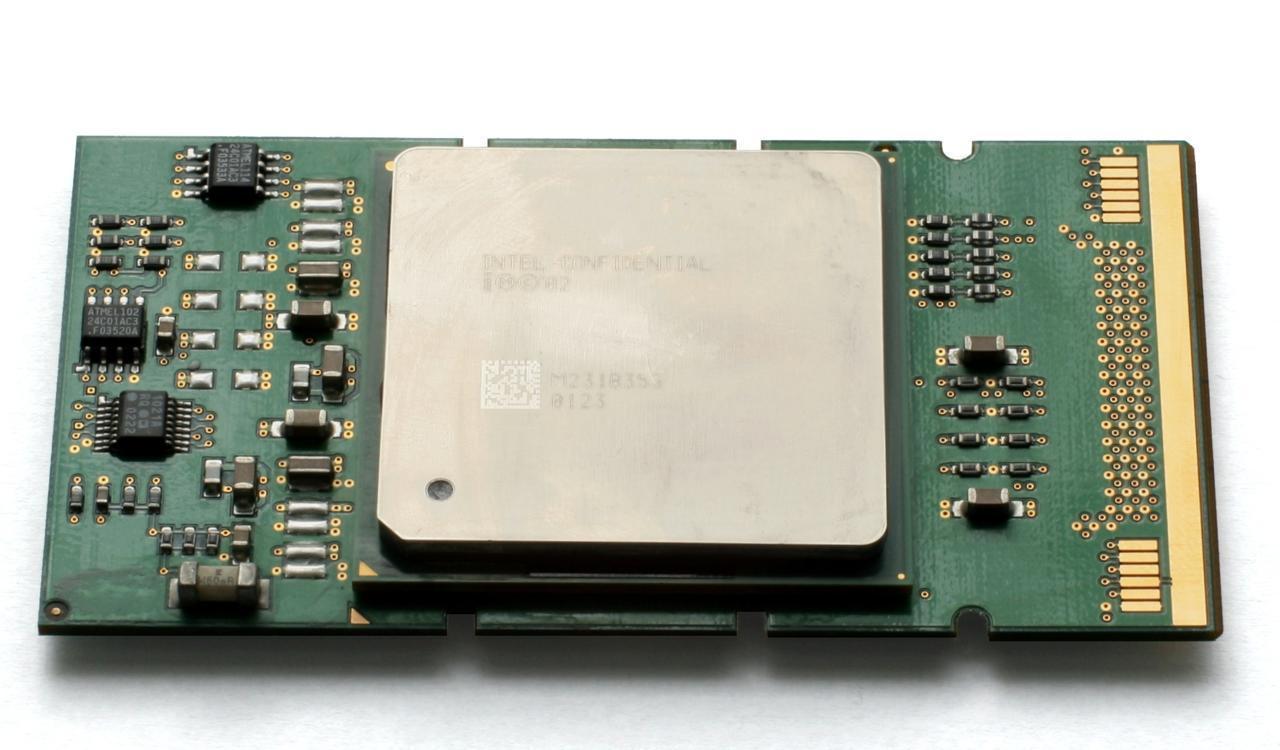

Tópico para a discussão do seguinte conteúdo publicado no Clube do Hardware: Merced: O Sucessor do Pentium II "Aprenda sobre o projeto P7 da Intel, codinome Merced, que acabou sendo lançado no mercado com o nome Itanium." Comentários são bem-vindos. Atenciosamente, Equipe Clube do Hardware https://www.clubedohardware.com.br

-

Processadores Para o Próximo Milênio - Parte 1

MZ Editora postou um tópico em Comentários de artigos

Tópico para a discussão do seguinte conteúdo publicado no Clube do Hardware: Processadores Para o Próximo Milênio - Parte 1 "Uma visão dos computadores antigos para entendermos onde vamos chegar." Comentários são bem-vindos. Atenciosamente, Equipe Clube do Hardware https://www.clubedohardware.com.br -

Tópico para a discussão do seguinte conteúdo publicado no Clube do Hardware: DVD - Arquitetura "Veja como funciona os aparelhos de DVD." Comentários são bem-vindos. Atenciosamente, Equipe Clube do Hardware https://www.clubedohardware.com.br

-

Tópico para a discussão do seguinte conteúdo publicado no Clube do Hardware: Processador Athlon "Aprenda sobre o funcionamento do processador Athlon da AMD. " Comentários são bem-vindos. Atenciosamente, Equipe Clube do Hardware https://www.clubedohardware.com.br

-

Continuando o estudo dos artigos anteriores, neste artigo exporemos a arquitetura de 64 bits da AMD. Ao longo dos últimos quatro meses, vimos o surgimento dos computadores, dos microcomputadores e a consolidação dos seus princípios fundamentais. Em seguida, estudamos como esses princípios evoluíram para o processamento paralelo e os novos problemas que daí surgiram. De posse dessas idéias, pudemos melhor compreender a complexidade das modernas máquinas de alto desempenho. Constatamos também que o processamento paralelo não está limitado às máquinas sofisticadas, mas é empregado em diversos processadores. Mesmo nossos “velhos” PCs-Pentium fazem uso de um paralelismo, mas a nível de instrução, ou seja, executam mais de uma instrução por vez. Agora, neste artigo e no próximo, abordaremos os processadores de 64 bits que irão impulsionar nossos próximos computadores pessoais. Os projetos da Intel e AMD são inovadores e, se as promessas forem cumpridas, em menos de um ano deverão estar nas prateleiras das lojas. Essas novas arquiteturas prometem levar o paralelismo ainda mais longe, fornecendo mecanismos para que os compiladores passem para as CPUs não só as instruções arrumadas de forma eficiente, mas principalmente como e quais podem ser executadas em paralelo. Quando se fala de CPUs de 64 bits, é importante elucidar uma certa confusão que se faz com processadores atuais. Devemos ter claro que todos os atuais processadores, Intel ou AMD, são CPUs de 32 bits. O Pentium 4 ou o Athlon têm barramento de dados de 64 bits, porém a arquitetura da CPU é de 32 bits. Neste artigo, vamos ver o que a AMD está planejando para a sua arquitetura de 64 bits. No mês que vem, será a vez da Intel. Arquitetura x86-64 da AMD Iniciamos com uma pergunta: como fazer a transição das CPUs de 32 bits para 64 bits? A AMD está respondendo a esta pergunta com uma arquitetura que, além do ambiente 64 bits, promete compatibilidade com todos os programas desenvolvidos para 16 e 32 bits. O objetivo é oferecer um caminho de baixo custo para que os usuários façam essa transição de forma bastante suave. Com uma arquitetura compatível com o mundo x86, os fabricantes de placas, de software e os usuários podem gerenciar mais facilmente seus investimentos. A ideia é oferecer uma ponte segura para a transição de 32 para 64 bits. A computação de 64 bits está voltada para aplicações que têm uma grande “fome” por memória, como as grandes bases de dados, as ferramentas CAD e as simulações que, de acordo com os recursos atuais, estão limitadas pelo espaço de endereçamento de 4 GB. Até há pouco tempo, dizia-se que as CPUs RISC ultrapassariam de forma definitiva as arquiteturas CISC. Porém, isso não aconteceu e as atuais máquinas CISC se equiparam às RISC, em termos de operações com inteiros, e já diminuíram bastante desvantagem que tinham em operações com ponto-flutuante. Por isso, afirma a AMD, os próximos ganhos de desempenho terão mais a ver com as técnicas de implementação (ex: paralelismo) do que com o conjunto de instruções: RISC, CISC-64 ou VLIW. Na verdade, há um certo abuso com esses nomes, pois as atuais CPUs x86 só têm uma casca CISC, sendo seu núcleo formado por máquinas RISC. A AMD está denominando sua nova arquitetura de “x86-64” e ela será iniciada com uma família de processadores que tem o nome código “Hammer”. As promessas apontam para a comercialização ainda no final deste ano. A estratégia de 64 bits da AMD é a extensão das atuais CPUs x86 para trabalharem em 64 bits, com a introdução do chamado Modo Longo. Essa solução é segura pois já foi empregada por ocasião da transição de 16 bits (CPUs 8088 e 286) para 32 bits (CPUs 386 e diante). Desde há muito tempo, as CPUs de 32 bits operam em dois modos. Quando em modo real, elas ficam iguais ao antigo 8088, porém, quando em modo protegido, elas oferecem recursos de 32 bits, junto com gerenciadores de tarefas e de memória. A arquitetura x86-64 oferece um novo modo denominado “Modo Longo”, em inglês “long mode”, que serve para colocar a CPU operando a 64 bits. Quando em Modo Longo, além dos recursos de 64 bits, são oferecidos registradores estendidos para 64 bits e, além disso, novos registradores foram adicionados. Passemos ao estudo desse novo modo. O Modo Longo é ativado através de um bit de controle chamado LMA, do inglês “Long Mode Active”. Quando o LMA estiver desativado, o processador operará no modo padrão x86 e será compatível com os sistemas operacionais e aplicativos de 16 e 32 bits, ou seja, será compatível com tudo que existe nos dias de hoje. Quando o LMA for ativado (Modo Longo), a extensão de 64 bits estará habilitada, oferecendo uma nova CPU de 64 bits. O Modo Longo é ainda dividido em dois submodos: o Modo 64-bits e o Modo Compatível. Esses dois submodos são controlados pelos bits D e L, presentes no descritor apontado pelo registrador CS (Segmento de Código). O Modo Compatível é interessante porque permite que, a nível de programa, se rodem aplicativos de 16 ou 32 bits dentro do Modo 64-bits. É algo semelhante ao modo virtual 86 dos processadores 386. A Figura 1 apresenta um quadro explicativo desses modos. Figura 1: Modos de operação da família x86-64. O antigo modo x86 (32 ou 16 bits) é denominado Modo Legal (LMA=0). Quando nesse modo, as CPUs x86-64 podem trabalhar com dados de 16 ou 32 bits. Note que, quando nesse modo, o estado do bit CS.L não tem significado, ou seja, ele é um “don’t care”. Quando colocado em Modo Longo 64-bits (LMA=1, CS.L=1 e CS.D=0), o tamanho padrão do operando é de 32 bits e o tamanho padrão para o endereçamento é de 64 bits. Com o uso de prefixos de instrução, o tamanho do operando pode ser alterado para 64 ou 16 bits e o tamanho do endereço para 32 bits. Se colocado no Modo Longo Compatível (LMA=1 e CS.L=0), passa a existir a compatibilidade binária com as aplicações escritas em 16 e 32 bits x86. Isso é interessante, pois um sistema operacional em Modo Longo pode rodar os atuais programas de 16 e 32 bits apenas colocando em zero o bit CS.L do descritor apontado pelo segmento de código desses aplicativos. No submodo Compatível, o bit CS.D continua a selecionar entre os modos de 16 e 32 bits. Deve ainda ser notado que, quando o processador está no Modo Legal, o estado do bit CS.L não tem significado, ou seja, é um “don’t care”. A Figura 2 apresenta os detalhes de programação dessa nova arquitetura. Figura 2: Características de programação da arquitetura x86-64 da AMD. Vamos agora dar uma olhada mais cuidadosa no Modo Longo. Como já foi visto, o Modo Longo permite o uso dos recursos de 64 bits, ao mesmo tempo que oferece o submodo Compatível para rodar aplicações de 16 ou 32 bits. Esse modo traz uma grande quantidade de recursos, que estão listados a seguir: Endereçamento virtual de 64 bits; Registradores estendidos para 64 bits; Adição de 8 registradores (R8-R15); Adição de 8 registradores para SIMD (XMM8-XMM15); Ponteiro de instruções com 64 bits; Modo de endereçamento absoluto (“flat”). A adição de novos registradores para operações SIMD torna disponível um total de 16 registradores multimídia. Os novos registradores de finalidade geral vêm a diminuir um pouco uma das deficiências da arquitetura x86, que é a pequena quantidade de registradores. Para definir sua lógica de registradores, a AMD simplesmente estendeu o esquema usado para os registradores de 16 e 32 bits. Assim, continua sendo possível acessar de forma fracionada os registradores herdados do antigo 8086. Por exemplo, o registrador RAX pode ser acessado como um único bloco de 64 bits, mas também é possível acessar somente sua metade inferior através do registrador EAX. Além disso, também está acessível uma porção de 16 bits (AX) e duas porções de 8 bits (AH e AL). É claro que AX é formado pela justaposição dos registradores AH com AL. Assim é mantida toda compatibilidade com os antigos ambientes x86. A Figura 3 ilustra esses possíveis fracionamentos. Figura 3: Esquema de fracionamento dos registradores herdados da arquitetura x86-64. Os avanços da tecnologia de integração e o aumento de velocidade do relógio deverão possibilitar um maior desempenho destas CPUs, mesmo quando operando no Modo Legal. Com essa arquitetura, a AMD espera oferecer um caminho tranqüilo para a transição de 32 para 64 bits. No passado, uma transição não tão tranqüila, devido ao novo modelo de memória, permitiu uma evolução dos 16 bits (8086 e 286) para os 32 bits (386 em diante). A AMD aposta que, ao invés de mudar completamente a arquitetura, o sucesso estará com quem mantiver a compatibilidade.

-

Desde 1994, Intel e HP vêm trabalhando numa proposta de 64 bits. Sua arquitetura deveria possibilitar aos processadores CISC um passo grande o suficiente para ultrapassar os processadores RISC. Usando a técnica denominada VLIW, ainda experimental na época, e criando o modelo EPIC, eles propuseram a arquitetura Merced, que ficou prometida para início do ano 2000. Como a conjuntura mudou, os processadores Pentium III e IV e o Athlon ofereceram desempenho excepcional, ultrapassando 1 GHz, e ainda devido ao preço elevado dessa nova arquitetura e a pouca disponibilidade de programas para 64 bits, o cronograma foi atrasado e o lançamento da arquitetura IA-64 deverá ocorrer somente neste ano. A sigla VLIW significa “Palavra de Instrução Muito Grande”, do inglês “Very Large Instruction Word”. Processadores que usam essa técnica acessam a memória transferindo longas palavras de programa, sendo que, em cada palavra, estão empacotadas várias instruções. No caso da IA-64, são usadas três instruções para cada pacote de 128 bits. Como cada instrução tem 41 bits, sobram 5 bits que são usados para indicar os tipos de instruções que foram empacotadas. A Figura 1 apresenta o esquema de empacotamento das instruções. Esse empacotamento diminui a quantidade de acessos à memória, cabendo ao compilador a tarefa de agrupar as instruções de forma a tirar o melhor proveito da arquitetura. Figura 1: Empacotamento das instruções usada na arquitetura IA-64. Como já foi dito, o campo de 5 bits, rotulado como “Indicador”, serve para indicar os tipos de instruções empacotadas. Esses 5 bits oferecem 32 tipos de empacotamentos possíveis que, na verdade, são reduzidos para 24 tipos, já que 8 não são utilizados Cada instrução usa um dos recursos da CPU, que estão listados a seguir, e que podem ser identificados na Figura 2: Unidade I: números inteiros; Unidade F - operações a ponto-flutuante; Unidade M - acessos à memória; e Unidade B - tratamento de desvios. A arquitetura que a Intel propõe para executar essas instruções, que foi denominada Itanium, é versátil e promete desempenho através da execução simultânea (paralela) de até 6 instruções. A Figura 2 apresenta o diagrama em blocos desta arquitetura que faz uso de um “pipeline” de 10 estágios. Figura 2: Diagrama em blocos da CPU Itanium (arquitetura IA-64). As arquiteturas IA-64 recebem a sigla EPIC, do inglês “Explicit Parallel Instruction Computing”, que é traduzida como “Computação com Paralelismo de Instruções Explícito”. Com essa sigla, a Intel quer dizer que o compilador será o grande responsável por determinar e explicitar o paralelismo presente nas instruções a serem executadas. Isto é uma combinação de conceitos chamados de especulação, predicação e paralelismo explícito. A seguir, estudaremos rapidamente cada um deles. O Paralelismo a Nível de Instrução (IPL - “Instruction Level Parallelism”) é a habilidade de executar múltiplas instruções ao mesmo tempo. Como já vimos, a arquitetura IA-64 permite empacotar instruções independentes para serem executadas em paralelo e, por cada período de relógio, é capaz de tratar múltiplos pacotes. Devido ao grande número de recursos em paralelo, tais como grande quantidade de registradores e múltiplas unidades de execução, é possível ao compilador gerenciar e programar a computação em paralelo. Os compiladores usados para as arquiteturas tradicionais são limitados em sua capacidade especulativa porque nem sempre há como ter certeza se a especulação será corretamente gerenciada pelo processador. A arquitetura IA-64 permite ao compilador explorar a informação especulativa sem sacrificar a correta execução de uma aplicação. A arquitetura IA-64 tem mecanismos denominados indicador de instruções, sugestões para desvios e cache, que permitem ao compilador enviar ao processador informações obtidas durante o tempo de compilação. Essas informações minimizam as penalidades advindas dos desvios e ausências de cache (“cache misses”). Existem dois tipos de especulação: a de dados e a de controle. Com a especulação, o compilador antecipa uma operação de forma que sua latência (tempo gasto) seja retirada do caminho crítico. A especulação é uma forma de permitir ao compilador evitar que operações lentas atrapalhem o paralelismo das instruções. A especulação de controle é a execução de uma operação antes do desvio que a precede. Por sua vez, a especulação de dados é a execução de uma carga da memória (“load”) antes de uma operação de armazenagem (“store”) que a precede e com a qual pode estar relacionada. Com a “predicação”, do inglês “predication”, marca-se com predicados todos os ramos dos desvios condicionais que, em seguida, são despachados para a execução em paralelo, porém, executa-se apenas os que forem necessários. Assim, é possível preparar a execução das instruções antes mesmo de se ter resolvido o desvio condicional. Além da remoção de desvios através do uso de predicados, na arquitetura IA-64, existe ainda uma série de mecanismos que devem diminuir o erro na predição dos desvios e o custo quando este erro acontece. A arquitetura IA-64 traz uma grande quantidade de registradores. São 128 registradores gerais (inteiros), 128 registradores de ponto-flutuante, 64 registradores de 1 bit, para os predicados, e diversos outros registradores para configuração, gerenciamento e monitoração do desempenho da CPU. Para finalizar, vemos que a Intel promete compatibilidade com os aplicativos de 32 bits (IA-32). Eles deverão rodar sem qualquer alteração desde que o sistema operacional e o “firmware” tenham recursos para isso. Deverá ser possível rodar aplicativos no modo real (16 bits), modo protegido (32 bits) e modo virtual 86 (16 bits). Com isso, eles querem dizer que a CPU poderá operar no modo IA-64 ou modo IA-32. Existem instruções especiais para transitar de um modo para outro, como mostrado na Figura 3. Figura 3: Modelo de transição dos conjuntos de instruções. As três instruções que fazem a transição entre os conjunto de instruções são: JMPE (IA-32): salta para um instrução de 64 bits e muda para o modo IA-64; br.ia (IA-64): desvia para uma instrução de 32 bits e muda para o modo IA-32; Interrupções transicionam para o modo IA-64, permitindo assim o atendimento de todas as condições de interrupção e rfi (IA-64): é o retorno de interrupção; o retorno se dá tanto para uma situação IA-32 quanto para uma IA-64, dependendo da situação presente no momento em que a interrupção for invocada. Com este artigo e com o anterior, que abordaram as arquiteturas de 64 bits da Intel e AMD, terminamos de falar sobre os processadores para o início do milênio. É importante citar que já existem máquinas rodando versões 64 bits do Windows e Linux. Por ora, mais que o desempenho, o que mais nos preocupa é a compatibilidade com nossos programas atuais. Realmente, há que se comprovar o quanto essas arquiteturas de 64 bits serão compatíveis com nossos programas de 32 ou 16 bits. Esperamos que, em menos de um ano, já tenhamos resposta para essa inquietude. Para finalizar essa parte de CPUs de 64 bits, é muito bom ver o quanto as duas empresas disputam o mercado dos processadores de alto desempenho. Isso nos garante o acesso a computadores cada vez mais maravilhosos e baratos. Concluindo, gostaríamos de comentar o enorme espaço que ainda existe para a evolução da eletrônica e conseqüentemente para a evolução dos computadores. Mais importante que o surgimento dos supercomputadores, essa nova era será marcada pela permeabilidade dos computadores. Será a era dos computadores invisíveis. Eles estarão presentes em quase todo dispositivo moderno. No momento, eles habitam nossos televisores, fornos de microondas, carros, relógios, aparelhos de som, DVD, etc.. Num futuro próximo, eles invadirão a geladeira, a torradeira, o aparelho de ar condicionado e todos nos aparelhos de uso cotidiano. Já ultrapassamos a era da eletrônica barata e estamos entrando na era da inteligência barata.

-

Na parte anterior, vimos algumas das máquinas mais velozes do planeta e também as promessas da computação quântica. Continuando, apreciaremos agora os computadores Cray, máquinas que sempre foram sinônimo de alto desempenho, e também alguns processadores que são interessantes, não pelas suas velocidades estonteantes, mas sim pela forma distinta de suas soluções. Computadores Cray É impossível falar de supercomputadores sem citar o pionerismo das máquinas fabricadas por Seymour Cray, que já usavam o conceito de processamento vetorial. Seu primeiro supercomputador foi o CRAY-1, fabricado em 1976. Era capaz de atingir o pico de 133 Megaflops. Em 1985, lançou o Cray-2, com o desempenho de 1,9 Gigaflops. Na época, esse computador tinha a maior memória do mundo: 2 Gigabytes. Quantidade gigantesca, mesmo para os parâmetros atuais. Após esses marcos, citamos as principais máquinas que a empresa Cray comercializa nos dias de hoje. Começamos com o Cray T-90, que usa até 32 processadores vetoriais em paralelo e chega a 60 Gigaflops. Em seguida, está o Cray T3E, que oferece até 2048 processadores, permitindo alcançar 2,5 Teraflops e que, em breve, será substituído pelo Cray SV2, ainda em fase de projeto. Finalmente, temos o Cray muita, (“MultiThread Architecture”), que pretende diminuir o trabalho de programação paralela ao oferecer vetorização e paralelização automáticas. O atual topo de linha é o Cray SV1, que traz solução para os conflitantes problemas de desempenho, preço e escalabilidade. Os supercomputadores, como é de se esperar, são máquinas caras mas que oferecem um grande desempenho. Essa característica os torna quase inacessíveis para as empresas menores. Fica então o dilema: ou gasta-se muito dinheiro e compra-se um computador de alto desempenho, ou então economiza-se dinheiro e tenta-se satisfazer-se com máquinas de desempenho inferior. Pensando nisso, a Cray projetou uma máquina escalável, cujo desempenho, de acordo com as necessidades e orçamento do cliente pode ir desde 1,2 Gigaflops até 1 Teraflops (1.000 vezes o desempenho inicial). Esse computador pode usar desde um processador (4,8 Gigaflops) até centenas de processadores, quando então atinge a marca de 1 Teraflops. São empregados dois tipos de processadores: um processador de alto desempenho (4,8 Gigaflops), chamado de MSP, e um processador convencional (1,2 Gigaflops). Até 6 MSP e até 8 processadores convencionais formam um nó. O sistema pode chegar até 32 nós, resultando em 1 Teraflops. A Figura 1 ilustra a escalabilidade desse computador. Figura 1: Escalabilidade do CRAY SV1. Em 22 de setembro de 1999, a Cray assinou um contrato com diversas agências americanas, entre elas a conhecida NSA (“National Security Agency”), aquela que trata, dentre outros temas, das limitações na exportação de programas de criptografia, para construir o SV2, que substituirá o Cray T3E. Este novo computador contará com novos processadores vetoriais e pretende atingir algumas dezenas de Teraflops. A tabela a seguir apresenta uma comparação de velocidade entre os principais computadores Cray. Figura 2: Desempenho (em Gigaflops). Abordemos agora alguns processadores que trazem novidades interessantes. A Sun Microsystems, fabricante das conhecidas estações Sun, está inovando o mercado da informática com seu processador MAJC, que em inglês se pronuncia “magic”. A sigla MAJC significa Arquitetura Microprocessada para Computação em Java, do inglês “Microprocessor Architecture for Java Computing”. De acordo com a Sun, os dados que os processadores dos servidores de rede tratam nos dias de hoje estão muito diferentes dos dados das décadas de 70 e 80. Este fato motiva as duas principais arquiteturas atuais: uma com conjunto complexo de instruções (CISC) e a outra com conjunto reduzido de instruções (RISC). Antigamente, por exemplo em uma operação de atualização de saldo, os dados que chegavam ao servidor eram utilizados imediatamente. Os servidores atuais, entretanto, antes da atualização, devem tratar primeiro da compactação e criptografia deles (e talvez até o comando de voz), para só depois realizar a operação de crédito. Isso tudo deve ser feito na taxa do fluxo de dados das redes de alta velocidade. Assim, nos modernos sistemas, os processadores devem estar aptos não só a receber os dados a taxas elevadas, mas também aptos a processá-los nesta mesma taxa. As principais exigências de hardware são velocidade de I/O e capacidade de processamento. O processador deve entrar no fluxo de dados sem gerar atrasos, ou seja, ele recebe os dados a taxas elevadas, os processa e os envia adiante nessa mesma taxa elevada. A primeira implementação da família, o MAJC-5200, tem a interface de I/O operando a 10 GB/s, quando o usual na maioria dos processadores é 1 GB/s, e sua a capacidade de processamento vem de duas CPUs, cada uma com 4 unidades funcionais VLIW (“Very Large Instruction Word”) que, além dos recursos usuais, operam como processadores de sinais digitais (DSP-“Digital Signal Processor”) e como processadores vetoriais SIMD. A CPU, como pode ser vista na Figura 3, possui 4 Unidades Funcionais (FU), numeradas de 0 até 4. Cada Unidade é um processador RISC. A UF0 é um pouco diferente das demais, pois ela é responsável por tratar da leitura e escrita de dados, que acontece através da Unidade de Carga e Armazenamento, e ainda por controlar o fluxo das operações (saltos). Por ser uma CPU tipo VLIW, as instruções de 32 bits vêm agrupadas em pacotes com até 4 instruções, 128 bytes no total, e cada uma é distribuída para uma Unidade Funcional. Se não houver interdependência, são realizadas até 4 operações por vez. O compilador é responsável por preparar o fluxo de instruções de forma a reduzir a interdependência. De acordo com a Figura 3, as instruções vêm do Cache e seguem para o Buffer de Instruções, daí passam pelos Decodificadores, têm seus Registradores acessados e vão para as Unidades Funcionais. Já os resultados são devolvidos aos Registradores graças ao Estágio de Contra-Escrita. O compartilhamento dos resultados entre as Unidades Funcionais é possível graças ao Estágio de Contra-Escrita, mas consome um ciclo. Entre UF0 e UF1, existe uma conexão que permite esse compartilhamento no mesmo ciclo de relógio. A CPU possui 224 registradores lógicos, divididos em 96 globais, que podem ser acessados por qualquer Unidade Funcional, e 32 particulares para cada UF. A Unidade de Carga e Armazenamento é responsável por gerenciar todas as operações entre a memória e os registradores. Está disponível um conjunto completo de instruções para operações inteiras e de ponto-flutuante. As unidades de 1 a 3 podem executar operações do tipo multiplica e acumula em um único ciclo. Tais instruções são fundamentais para a implementação de filtros digitais. As unidades podem operar juntas implementando um ambiente de execução tipo SIMD. Com tais instruções e operando a 500 MHz, essa CPU é capaz de obter um desempenho de 6,16 Gigaflops. Figura 3: A CPU MAJC. A Figura 4 apresenta o diagrama em blocos do processador MAJC-5200, que possui duas CPUs idênticas às mostradas na Figura 3. Deve-se notar que o cache de dados é compartilhado entre as duas CPUs, porém existe um cache de instrução para cada uma. A capacidade para aceitar altas taxas de bits deve-se à quantidade de interfaces, cada uma delas com seu próprio controlador. A memória principal é do tipo Rambus (DRDRAM) e trabalha a 1,6 GB/s. A Ponte PCI oferece recursos para DMA e I/O, a taxas de até 264 MB/s. Existem duas outras interfaces, a UPA Norte e a UPA Sul, que podem operar a até 4 GB/s. A porta UPA, que em inglês significa “Universal Port Architecture”, destina-se a interfacear dados com altas taxas, como por exemplo vídeo. Além disso tudo, existe um Processador Gráfico para, dentre outras coisas, fazer a descompressão de geometria 3D em tempo real. Figura 4: Diagrama em blocos da arquitetura MAJC-5200. Nessa arquitetura, a Sun usou o que seus engenheiros chamam de “processamento espaço-tempo”, mas que também pode ser rotulado como processamento especulativo. Graças a isso, os programadores não precisam de preocupar-se em explicitar o paralelismo de seus programas, por que essa tarefa será especulada pela máquina virtual Java. A máquina virtual examina o programa e especula se dois métodos podem rodar em dois processadores, despachando-os ao mesmo tempo. Assim, ela envia os dois métodos para dois processadores distintos, sendo que um deles (o segundo) rodará em separado, usando o que se chama de espaço de memória especulativa. Ao término do processamento, se tudo correu bem e não houve violação de dependência de dados então a área especulativa é fundida com a memória principal e o programa segue adiante. Entretanto, se tiver havido dependência entre os dados, o segundo processo é inutilizado e sua memória descartada. Esse processador não tem desempenho comparável com os processadores aqui analisados, já que ele chega apenas a 50 MIPS (mega instruções por segundo). Porém, o que o torna notável é o fato de ser totalmente construído em PLD, sigla que significa dispositivos lógicos programáveis, do inglês “Programmable Logic Device". Um dispositivo lógico programável é um circuito digital que o usuário pode configurar de forma a solucionar seu problema. É como se fosse um Lego Digital onde o usuário junta as peças para construir o circuito digital que necessita. O que a Altera fez foi fornecer, junto com seu Lego Digital, um mapa que ensina a construir um processador RISC. Note que o usuário pode alterar esse mapa e construir uma CPU RISC específica para sua necessidade. O que é mais interessante é que sobram peças de Lego dentro da caixa, ou seja, sobram circuitos programáveis dentro do chip e estes podem ser usados para implementar ainda outros circuitos digitais. Essa CPU RISC pode chegar a 50 MIPS, possui um conjunto de instruções de 16 bits, barramento de dados de 16 ou 32 bits, um “pipeline” de 5 estágios e em média executa uma instrução por ciclo. Ela usa, conforme a implementação, de 2% a 25% dos dispositivos programáveis, o que deixa bastante recurso para o usuário expandi-la colocando outros periféricos mapeados em memória, dispositivos de leitura e escrita mapeado nos bancos de registradores, ou ainda, blocos funcionais dentro da CPU. Em suma, o usuário pode modificar essa CPU, talhando-a para sua necessidade específica. A Figura 5 apresenta um diagrama em blocos do núcleo Nios, que consiste da CPU, de uma interface com memória estática ou dinâmica, de um temporizador, de uma UART, de uma PIO e de uma linha de interrupção. Além disso tudo, também são oferecidos compilador C/C++, montador e depurador. Figura 5: Diagrama em blocos da CPU RISC Nios da Altera, ressaltando que boa parte ainda está disponível. Nesta parte do artigo, continuamos a ver que o processamento paralelo infiltra-se nas mais diversas CPUs, oferecendo cada vez mais desempenho e exigindo compiladores sofisticados. O compilador já era importante para as máquinas RISC, mas agora, perante essas novas CPUs, ele assume um papel mais fundamental, pois passa a ser responsável por sugerir a especulação e a execução paralela. A Intel e a AMD também empregam bastante o processamento paralelo nas suas arquiteturas de 64 bits, como poderá ser constatado na continuação deste artigo. Verificamos ainda que os fabricantes de supercomputadores estão preocupados com o cliente intermediário e oferecem para máquinas acessíveis, mas que podem ser expandidas de forma a atingir grande desempenho. Finalmente, vemos chegar a era na qual o usuário pode projetar seu processador. É claro que isso é interessante não tanto para o usuário comum, mas sim para aqueles que fabricam equipamentos com processadores incorporados, como é o caso dos fabricantes de celulares, máquinas fax, impressoras e até mesmo aparelhos de televisão. No passado, era necessário ajustar o projeto aos processadores disponíveis no mercado. Agora, já é possível comprar a descrição do processador e modificá-lo de forma a atender, de forma minuciosa, a todas suas necessidades do projeto. Na próxima parte deste artigo veremos as soluções que Intel traz em sua arquitetura de 64 bits (IA-64). Sites Seymour Cray: http://americanhistory.si.edu/csr/comphist/cray.htm Seymour Cray: http://www.cgl.ucsf.edu/home/tef/cray/tribute.html MAJC: http://www.sun.com/microelectronics/MAJC/5200.html Altera-Nios: http://altera.com/html/products/nios.html

-

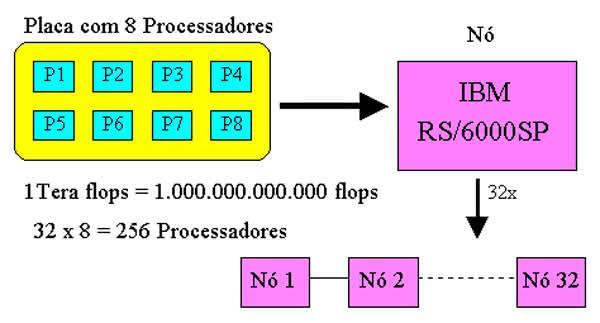

Na primeira parte deste artigo vimos uma pequena e rápida resenha histórica sobre os computadores. A parte anterior foi dedicada ao estudo da evolução da arquitetura serial para a arquitetura paralela. Agora, nesta terceira parte, vamos analisar algumas arquiteturas paralelas que foram propostas pela IBM. Veremos, não só o mais poderoso computador da atualidade, como também o projeto mais ambicioso do momento. Faremos ainda uma breve exposição sobre os computadores quânticos. Como vamos comparar velocidade de máquinas de alto desempenho, necessitaremos de uma unidade de medida. Em tais casos, a velocidade é medida pela quantidade de operações de ponto-flutuante por segundo, abreviado por flops (do inglês “float operations per second”). Como os valores são elevados, utilizam-se os multiplicadores listados na tabela ao final deste artigo. Assim preparados, iniciamos nosso estudo com um computador enxadrista. A máquina chamada “Deep Blue”[1] ainda é o mais poderoso computador voltado para o jogo de xadrez. Mas, o que será que tem de interessante uma máquina que joga xadrez? Muita coisa quando esta máquina possui uma arquitetura paralela capaz de realizar 1.000.000.000.000 operações de ponto-flutuante por segundo (1Teraflops). A arquitetura é bem simples: o “Deep Blue” está montado sobre estações de trabalho IBM RS/6000SP (P2SC). Cada estação é um nó e cada nó usa um placa microcanal contendo 8 processadores VLSI. Como são empregados 32 nós, chega-se a um total de 256 processadores trabalhando em paralelo, como mostrado na Figura 1, onde uma letra “P” é usada para representar cada processador. Figura 1: Arquitetura do Computador “Deep Blue” com seus 256 processadores. Tal arquitetura, capaz de analisar 200 milhões de posições de xadrez por segundo, duelou com o mestre Garry Kasparov, cuja capacidade de análise é de aproximadamente 3 posições por segundo. Realmente, foi uma batalha desigual. No dia 11 de maio, foi iniciada a disputa de 6 partidas, que terminou em 3,5 x 2,5 a favor do “Deep Blue”. Deve-se notar que Kasparov ainda foi capaz de ganhar a primeira e empatar três, perdendo apenas duas partidas. Kasparov, pelo segundo lugar ganhou US$ 400.000,00, enquanto que o “Deep Blue”, o vencedor, levou US$ 700.000,00 (mas infelizmente ele não teve onde gastar). Figura 2: Kasparov versus “Deep Blue”. A habilidade do “Deep Blue” em jogar xadrez vem da chamada “função de avaliação”. Esta função é um algoritmo que mede a qualidade de uma dada posição de xadrez. Posições com valores positivos são boas para as brancas, enquanto que aquelas com valores negativos são boas para as pretas. Se o cômputo total é positivo, as brancas estão em vantagem. A função de avaliação leva em conta 4 valores que são básicos para o xadrez: material, posição, segurança do Rei e tempo. O material é calculado segundo o valor das peças, o peão vale 1 e assim por diante até a Rainha que vale 9. O Rei, é claro, está além desses valores pois sua perda implica em derrota. A posição é calculada ao olhar suas peças e contar o número de posições seguras que eles podem atacar. A segurança do Rei é medida em função de sua capacidade defensiva. O tempo está relacionado com o desenvolvimento do jogo sobre o tabuleiro. Além disso tudo, o “Deep Blue” não usa força bruta ao avaliar as posições, mas sim seleciona alguns caminhos com bom potencial e elimina as buscas irrelevantes. Aproveitamos ainda para elucidar alguns pontos sobre este embate. O “Deep Blue” não usa inteligência artificial (IA) e tampouco aprende enquanto joga com seu oponente. Ao invés disso, ele trabalha como um sistema especialista que analisa seu vasto sistema de informações. Por exemplo, ele consulta sua base de dados com todas as aberturas dos últimos 100 anos e então calcula qual a melhor resposta ao movimento do oponente. Ele não pensa, mas sim, apenas reage e foi aí onde Kasparov tinha sua vantagem. Mas é claro que, com todos esses recursos, o “Deep Blue” é de certa forma “força bruta” contra a inteligência de Kasparov, que teve que jogar contra os fantasmas de todos os grandes mestres do passado. Além disso, a máquina nunca esquece ou se distrai. Para terminar este tópico, perguntamo-nos por que tanto dinheiro para jogar xadrez? O principal objetivo não está no jogo, mas sim na busca de uma arquitetura rápida o suficiente para apresentar resultados práticos. Para isso, o xadrez é um excelente desafio, pois, com suas 64 células, oferece um problema matemático extremamente complexo. Ao provar sua eficiência nessa área, a IBM demonstrou ser capaz de oferecer computadores para os problemas que ainda desafiam as atuais máquinas. E, no dia seguinte à vitória, suas ações subiram. O mais rápido computador da atualidade chama-se “Blue Pacific” e foi entregue em 28 de outubro de 1998. O termo ASCI vem de “Accelerate Strategic Computing Iniciative”, traduzido como “Iniciativa para Aceleração da Computação Estratégica”, que é o nome do programa do Departamento de Energia Norte-Americano para acelerar os avanços nas tecnologias necessárias para simular numericamente dispositivos nucleares, eliminando assim a necessidade do teste físico. Ele emprega 5.856 processadores que, operando cada um a cerca de 333 MHz, entregam uma potência de aproximadamente 4 Teraflops, ou, em outros termos, é 15.000 vezes mais rápido que um PC convencional, consumindo o equivalente a 324 secadores de cabelo. Uma pessoa com um calculadora de mão levaria 63 mil anos para realizar as operações que esse computador faz em 1 segundo. A tabela a seguir resume suas principais características. Processadores 5.856 Nós 1.464 Memória 2,6 Terabytes Armazenagem 75 Terabytes Desempenho 3,88 Teraflops Potência 486 kW Preço US$ 94 milhões Em 6 de dezembro de 1999, a IBM anunciou uma pesquisa de US$ 100 milhões com o objetivo de construir um computador que será 500 vezes mais poderoso que o mais rápido computador da atualidade. Esse novo computador, apelidado de “Blue Gene” será capaz de ultrapassar a marca de 1 quadrilhão de operações por segundo, ou seja, 1 Petaflops (10^15 flops). Essa marca o torna 1.000 vezes mais poderoso que o “Deep Blue” e cerca de 2 milhões de vezes mais rápido que um PC topo de linha. Essa maciça capacidade de processamento será usada inicialmente para modelar o “dobramento” das proteínas humanas. As proteínas controlam todos os processos celulares do corpo humano. Formadas por cadeias de aminoácidos, são unidas como anéis em uma corrente e dobram-se de formas altamente complexas. Sua forma tridimensional determina sua função. Qualquer mudança na forma altera dramaticamente a função da proteína. Mesmo uma pequena alteração no processo de dobragem pode transformar uma proteína desejável em uma doença. Assim, aprender mais sobre como as proteínas são dobradas deverá possibilitar aos pesquisadores médicos uma melhor compreensão das doenças e, em conseqüência, de suas curas. A comunidade científica considera o problema de dobragem das proteínas como um dos grandes desafios científicos da atualidade e sua solução somente pode ser alcançada com a tecnologia de computação de alto desempenho que, com certeza, terá grande impacto científico e econômico. A expectativa da IBM é atingir os Petaflops em 5 anos, um terço do que seria esperado segundo a Lei de Moore. A IBM denomina sua abordagem para este computador de SMASH, “Simple, Many and Self-Hearing”, que seria traduzido como “Simples, Muitos e Auto-Curativo”. Três tópicos distinguem essa arquitetura SMASH: Redução dramática do número de instruções, permitindo que os processadores sejam rápidos, de baixo consumo e ocupem pouca área do CI; Facilidade no processamento maciçamente paralelo, permitindo mais de 8 milhões de “threads”; Garantia de um computador auto-estável e auto-curativo, sobrepujando falhas de processadores e de “threads”. O “Blue Gene” consistirá de mais de 1 milhão de processadores, cada um capaz de oferecer 1 bilhão de operações por segundo, ou seja, 1 Gigaflops, como está mostrado na Figura 3. Trinta e dois desses processadores serão integrados em um único CI, resultando em 32 Gigaflops. Uma placa de 2 pés por 2 pés receberá 64 CIs, levando a 2 Teraflops. Somente essa placa já é capaz de igualar o desempenho do “Blue Pacific”, que tem 8.000 pés quadrados. Oito dessas placas (16 Teraflops) serão colocadas em “racks” de 6 pés. Finalmente 64 “racks” constituirão o estado final do computador, ocupando uma área menor que 2.000 pés quadrados. Figura 3: Arquitetura do “Blue Gene”, com seu 1 milhão de processadores. Agora teremos a sensação de que entramos no campo da ficção científica. Os computadores tradicionais trabalham com elementos básicos que podem assumir dois estados (ou dois bits): 0 ou 1. Normalmente, usam-se transistores ou “flip-flops” para representá-los. Olhando para o lado da física atômica, uma partícula quântica, como o elétron ou núcleos atômicos, pode existir em dois estados: com o “spin” para cima ou para baixo. Ora, isto constitui um bit quântico ou “qubit”. Quando o spin está para cima, o átomo pode ser lido como 1 e, quando o spin está para baixo, é lido como 0. Os qubits diferem dos bits tradicionais porque um núcleo atômico pode estar num estado de superposição, representando simultaneamente 0 e 1 e tudo o mais que existe entre esses valores. Mais ainda, sem a interferência do ambiente externo, os spins podem se “relacionar” de tal forma que efetivamente conectam os qubits de um computador quântico. Dois átomos “relacionados” atuam em conjunto: quando um está na posição para cima e o outro é garantido estar na posição para baixo. A combinação de superposição e “relacionamento” é o que permite a um computador quântico ter um enorme poder de processamento, possibilitando-o a realizar cálculos de forma maciçamente paralela e de forma não linear. Para certos tipos de cálculos, como por exemplo os complexos algoritmos para criptografia, um computador quântico pode realizar bilhões de cálculos em um único passo. Ao invés de resolver o problema pela adição ordenada de todos os números, um computador quântico poderia adicionar todos os números ao mesmo tempo. Assim, pela interação de um com o outro, quando isoladas do ambiente externo, os qubits podem realizar certos cálculos de forma exponencialmente mais rápida que os computadores convencionais. Diz-se que o computador quântico começa onde a Lei de Moore termina. Em 15 de agosto de 2000, um time da IBM demonstrou um novo computador quântico com 5 qubits, composto portanto por 5 átomos (de flúor) fixados em uma molécula especialmente projetada de forma a permitir que os qubits (spin dos núcleos) “relacionem” entre si. Esses qubits são programados por pulsos de rádio-freqüência e detectados por meio de ressonância nuclear magnética, semelhante ao usado em hospitais. Esse computador de 5 qubits foi capaz de resolver um problema de determinação de ordem de um sistema, ou seja, a determinação do período de uma função. Os computadores convencionais calculam a solução usando iterações passo-a-passo com os valores da função até que eles comecem a repetir. O computador quântico faz isso com um novo enfoque. Por natureza, eles representam simultaneamente todos os possíveis valores da variável de entrada e, portanto, com um único passo pode analisar todos os possíveis valores da função. Apesar do potencial dos computadores quânticos ser gigantesco e encorajador, os desafios ainda são enormes. O atual computador de 5 bits é um mero instrumento de pesquisa. Ainda faltam muitos anos de trabalho para que os computadores quânticos se tornem comerciais. Os prognósticos indicam que eles deverão ter pelo menos 12 bits para poderem resolver problemas do mundo real. Espera-se que, no futuro, tais computadores venham a trabalhar como processador auxiliar para problemas matemáticos de difícil solução. Com certeza processamento de texto e Internet não são aplicações talhadas para um computador quântico. A ideia do computador quântico não é recente, ela foi proposta na década de 1970. Observa-se claramente que os grandes computadores caminham para o processamento paralelo. Basicamente, o poder está vindo, não dos megahertz do processador, mas da quantidade de processadores que em conjunto resolvem um determinado problema. Isto significa que o tamanho do grão de processamento será cada vez menor e os processos cada vez mais acoplados. Vê-se também o uso intenso da arquitetura que Flynn (página anterior) classificada como MIMD. Como substituição para o atual modelo de processamento e esperança para os novos computadores, surge o processador quântico. No próximo número veremos alguns computadores Cray e estudaremos dois processadores simples, porém inovadores. Continue lendo: Processadores para o próximo milênio - parte 4 [1] “HAL’s Legacy”, David G. Stork (Editor). Sites Deep Blue: http://www.research.ibm.com/deepblue/meet/html/d.3.2.html Todas partidas Deep Blue vs Kasparov: http://www.ishipress.com/deepblue.pgn Blue Gene: http://www.research.ibm.com/news/detail/bluegene.html Blue Pacific: http://www.rs6000.ibm.com/hardware/largescale/SP/index.html Quântico: http://www.research.ibm.com/resources/news/20000815_quantum.html

-

Na primeira parte deste artigo abordamos alguns tópicos da história dos computadores. Continuando, vamos estudar os conceitos propostos por um dos nomes que apareceu neste histórico e, em seguida, abordaremos os principais tópicos sobre processamento paralelo. Postulados de von Neumann Von Neumann[1], que trabalhou no desenvolvimento do ENIAC e posteriormente empregou sua experiência no projeto do IAS (1952), elaborou as idéias e os conceitos que nortearam a arquitetura dos computadores até os dias de hoje. Seu entendimento é essencial para apreciarmos a atual evolução dos computadores. Iniciemos constatando, de forma óbvia, que as máquinas que usamos nas nossas casas possuem quatro elementos básicos: a CPU, a memória, os dados e as instruções (ou programas). A partir daí, apresentamos os três postulados básicos de von Neumann, que no momento podem parecer triviais, mas que não o eram na década de 50: 1. Um único controle centralizado (uma só CPU); 2. Uma única memória para dados e instruções; e 3. As instruções devem fazer operações elementares sobre os dados. Cerca de 90% dos computadores atuais usam esses postulados e por isso são chamados de “Arquitetura de von Neumann”, ou “Arquitetura Serial”, pois empregam um único processador. Essa arquitetura, aliada aos avanços da microeletrônica, ofertou-nos o atual mercado de computadores, rápidos e baratos. Porém, tal arquitetura enfrenta um limite de velocidade que é ditado pelas leis da física. O tempo que um sinal elétrico gasta para trafegar entre dois pontos de um circuito eletrônico é muito pequeno, porém não é igual a zero. Em outras palavras, isto corresponde a dizer que existe um limite para a velocidade de relógio das CPUs e, infelizmente, ele não está muito distante. Como então continuar com a evolução dos computadores? Essa é a pergunta que tem ocupado a cabeça de muitos pesquisadores e desde a segunda metade desta década, várias soluções foram propostas. A principal resposta vem da comparação entre nosso cérebro e um processador. É sabido que o sinal elétrico trafegando por dentro de um CI é muito mais veloz que o trânsito de impulsos nervosos entre nossos neurônios. É claro que, para fazer operações numéricas, comparar e classificar, o computador é mais rápido. Mas, por outro lado, ele é inferior, pois não pensa, não inova e não aprende, apenas segue passos programados. Por exemplo, com um único olhar em uma sala identificamos imediatamente centenas de objetos. Já um computador, mesmo o mais sofisticado, apenas consegue identificar os objetos mais simples. Somos capazes de dirigir um carro e enquanto andamos por nossas (terríveis) estradas, temos habilidade para escolher o melhor caminho. Será que um computador pode dirigir um carro? Uma das experiências no MIT com um piloto computadorizado, que identificava a rua através das linhas paralelas do meio fio, revelou um grande escalador de árvores, pois ele confundia o contorno do meio fio com o contorno do caule das árvores. Como será que o cérebro consegue ser superior aos processadores, se o nosso neurônio é muito mais lento que um circuito eletrônico? A resposta é óbvia: porque temos vários bilhões de neurônios operando em paralelo. Ora, por que, ao invés de construirmos CPUs velozes e gigantescas, não usamos várias CPUs, simples e confiáveis, operando em paralelo? Chegamos assim à ideia básica do processamento paralelo, que é a esperança para o próximo milênio Sabemos então que devemos usar uma grande quantidade de processadores, mas como controlá-los de forma a que façam alguma coisa de útil? Existem grandes problemas! Para iniciar, vamos trabalhar o conceito de processamento paralelo através de um exemplo bem simples. Se um pedreiro constrói uma casa em um ano, então dois pedreiros constróem a mesma casa em meio ano. Este é conceito básico do processamento paralelo: a divisão das tarefas. Podemos seguir adiante e concluir que cem pedreiros gastam apenas 3,6 dias. Será isto um absurdo? É claro que há um limite, pois o trabalho dos pedreiros só será eficiente se estiverem perfeitamente sincronizados e equilibrados. Este ponto é importante: todos os pedreiros devem ter a mesma carga de trabalho. Em termos técnicos, usa-se a expressão “Balanceamento da Carga de Trabalho”. Esse balanceamento pode ser feito de dois modos. No primeiro modo, o trabalho de cada pedreiro é idêntico, ou seja, cada um faz 1/100 da casa. No outro modo é usado a especialização, ou seja, alguns pedreiros “viram” cimento enquanto outros assentam tijolos e outros tratam do encanamento, e assim por diante. Ao imaginarmos todas as tarefas que devam ser executadas para a construção da casa, fica claro que algumas delas não poderão ser paralelizadas. Imagine 100 pedreiros para assentar um porta, ou 100 pedreiros em cima da casa tentando montar o telhado. A casa acabaria por cair! Além disso, deve haver um limite para a quantidade de pedreiros que podem trabalhar em paralelo. A partir deste limite, quanto mais pedreiros colocamos, pioramos o desempenho e em conseqüência, aumentamos o tempo de construção. Temos então dois grandes problemas: até quanto podemos paralelizar uma tarefa e até quantos processadores devem ser alocados? A partir daí, surgem outras questões: como sincronizar esses processadores de forma a que um não repita o trabalho do outro e como garantir o balanceamento da carga de trabalho? Agora temos condições de entender porque se diz que as dificuldades presentes no projeto do hardware de máquinas paralelas não são tão complexas quando comparados com os problemas de sua programação. Diz-se que os computadores estão sempre uma geração atrasada em relação às nossas necessidades e os programas, duas gerações atrasadas. Em suma, um desafio maior que o projeto de supercomputadores é a sua programação. É muito difícil a tarefa de classificar computadores paralelos. Já foram feitas diversas sugestões. A classificação definitiva ainda está por vir. Porém, a que trouxe melhores resultados e ainda hoje é usada, é a proposta por Flynn[2]. Essa classificação está baseada em dois conceitos: fluxo de instruções e fluxo de dados. O fluxo de instruções está relacionado com o programa que o processador executa, enquanto que o fluxo de dados está relacionado com os operandos manipulados por essas instruções. O fluxo de instruções e o fluxo de dados são considerados independentes e por isso existem quatro combinações possíveis, como mostrado na Figura 1. Figura 1: Fluxo de instruções e dados. Nas Figuras 2 a 5 apresentamos os diagramas de blocos para essas 4 combinações. Nessas figuras, a sigla MM representa o “Módulo de Memória” e a sigla EP representa o “Elemento de Processamento”, ou seja, o processador. Essas quatro arquiteturas serão detalhadas a seguir. Figura 2: Arquitetura SISD (Single Instruction Single Data). Figura 3: Aquitetura SIMD (Single Instruction Multiple Data). Figura 4: Arquitetura MISD (Multiple Instruction Single Data). Figura 5: Arquitetura MIMD (Multiple Instruction Multiple Data). SISD - Instrução Única, Dado Único (Single Instruction Single Data) Essa arquitetura é usada nos computadores que temos em casa. Segue o proposto por von Neumann e é por isso denominada de “Arquitetura de von Neumann”, também chamado de computador serial. Temos um único fluxo de instruções (SI), caracterizado pelo contador de programa da CPU, que opera sobre um único dado (SD) por vez. A Figura 2 apresenta um diagrama de blocos ilustrativo deste caso. Apesar de serem representados como módulos separados, a memória de instruções e a memória de dados são, para este caso, a mesma. SIMD - Única Instrução, Múltiplos Dados (Single Instruction Multiple Data) De início esta arquitetura paralela pode parecer estranha, mas como será constatado adiante, ela não só é conhecida, como também já foi muito utilizada. Para facilitar o conceito de um computador que utilize uma única instrução operando sobre uma grande quantidade de dados, devemos consultar o diagrama da Figura 3. A arquitetura mostrada apresenta N processadores (EP), sendo que cada processador trabalha sobre um dado distinto, que vem de cada um dos N módulos de memória (MD). O ponto importante é que todos os processadores (EPi) trabalham sincronizados e executam todos a mesma instrução, ou seja, cada instrução é passada, ao mesmo tempo, para os N EPs. Assim, os processadores executam a mesma instrução, porém sobre um dado diferente. Como é fácil de concluir, um computador com essa arquitetura é capaz de operar um vetor de dados por vez. Vem daí seu nome de Computador Vetorial, ou “Array Processor”. Um grande exemplo desta arquitetura são os famosos computadores Cray. Outro exemplo é o conjunto de instruções MMX. Eles são muito usados quando um mesmo programa deve ser executado sobre uma grande massa de dados, como é o caso de prospeção de petróleo. Note que essa arquitetura não sofre com problemas de sincronização, pois existe um único programa em execução. MISD - Múltiplas Instruções, Dado Único (Multiple Instruction Single Data) Essa arquitetura é um pouco mais difícil de ser explicada. Tentemos imaginar como é que se pode fazer múltiplas operações (MI) sobre um mesmo dado (SD). Os próprios pesquisadores têm opiniões divergentes sobre esse assunto. Entretanto, não vamos entrar nesses debates teóricos. De forma simples, vamos estudar a Figura 4, onde pode ser visto que, apesar de existir um único fluxo de dados, existem vários dados sendo operados ao mesmo tempo. Essa figura é conhecida na literatura especializada com o nome de “pipeline” ou linha de produção. A figura mostra que N processadores operam sobre K diferentes dados. Façamos uma analogia com uma linha de montagem de carros. Vamos supor que um carro leve 6 horas para ser montado e que a tarefa de montagem possa ser dividida em 12 equipes, numeradas em seqüência de 1 até 12, cada uma gastando meia hora. É fácil de ver que não precisamos esperar que a última equipe termine de montar um carro para a equipe 1 inicie a montagem do carro seguinte. Na verdade, todas elas trabalham simultaneamente, montando vários carros ao mesmo tempo. Por isso, com alguma liberdade, é costume classificá-la de paralelismo temporal. Então, apesar do tempo de montagem consumir 6 horas, a saída da linha de produção entrega um carro a cada meia hora. Agora é fácil voltar aos computadores e ver que temos um único fluxo de dados (SD), porém vários instruções (MI) processam esses dados, ao mesmo tempo. MIMD - Múltiplas Instruções, Múltiplos Dados (Multiple Instruction Multiple Data) Essa é a arquitetura que esperaríamos encontrar em um computador paralelo. Temos vários dados (MD) sendo operados por vários instruções (MI), simultaneamente. Essa é a arquitetura mais usada pelos modernos supercomputadores. Nesse caso, é importante que os processadores possam se comunicar entre si para fazer a sincronização e trocar informações. Além disso, é necessário ter uma memória, chamada de global, onde todos processadores possam disponibilizar, para os demais, os resultados intermediários. A Figura 5 apresenta uma solução genérica para essa arquitetura MIMD. Note que agora temos N processadores e dois tipos de memória: a local e a global. A memória global pode ser acessada por qualquer um dos processadores, por isso existe a chamada “Estrutura de Comunicação”, que disponibiliza a memória global para qualquer um dos processadores. Uma única memória global criaria um grande gargalo, pois só um processador poderia acessá-la por vez. Por isso, a figura apresenta duas memórias globais e, com isso, dois processadores podem ser atendidos ao mesmo tempo. Para evitar uma quantidade excessiva de acessos a essa memória, os processadores possuem a chamada memória local, onde está a maioria das suas instruções e dos dados que devam ser operados. Essa memória local evita que a estrutura de comunicação se transforme num enorme gargalo. Os processadores precisam trocar informações e, no caso desta figura, a própria estrutura de comunicação se encarrega desta tarefa. Uma simples análise da arquitetura MIMD da Figura 5 mostra que agora existe um fluxo de múltiplos dados (MD) sendo operado por um fluxo de múltiplas instruções (MI). Agora sim é necessária a genialidade dos programadores, pois como conseguir que uma estrutura deste tipo, imagine 1.024 processadores, trabalhe de forma sincronizada para gerar algum resultado? Se já é difícil escrever e depurar programas seriais, imagine fazer isso em um computador com 1.024 diferentes programas trabalhando sobre 1.024 dados diferentes. Como medir o quanto se ganhou com a execução de uma tarefa em um computador paralelo? É intuitivo que devemos usar o tempo de execução para medir esse desempenho, já que nosso principal objetivo é aumentar a velocidade de processamento. Uma solução boa é verificarmos a relação entre os tempos gastos para executar essa tarefa em um computador serial e em um computador paralelo. A expressão a seguir é usada para o cálculo do Ganho de Velocidade, que é abreviado pela sigla GV. Por exemplo, uma determinada tarefa, quando executada em um computador convencional consome 200 s e quando executada em uma máquina paralela (24 processadores) consome 10 s, então o ganho de velocidade é GV = 200/10 = 20. Gostaríamos que o Ganho de Velocidade fosse igual à quantidade de Elementos de Processamento (EP) empregados, mas isso é raro de acontecer pois quando se escreve um programa para rodar em máquinas paralelas, invariavelmente se necessita colocar trechos extras (de programa) para sincronização dos diversos EP e troca de informações. Esses trechos extras recebem o nome de custo de paralelização. Dependendo da tarefa a ser executada, pode haver uma necessidade de sincronização e troca informações tão grande que venha a inviabilizar o processamento paralelo. O ideal é que um aumento no número de processadores traga um igual aumento de desempenho (GV). A Figura 6 apresenta 4 casos, onde se calcula o Ganho de Processamento em função do número de processadores. A curva em vermelho mostra o caso ideal, onde há um ganho linear em função do número de processadores. A curva em verde traz um caso mais real onde o ganho não acompanha a quantidade de processadores, ou seja, ao dobramos a quantidade de processadores, não dobramos o ganho de velocidade. A curva em azul traz um caso de saturação em 85 processadores, ou seja, é inútil utilizar mais do que 85 processadores. A curva em negro apresenta um caso ainda pior, pois nota-se que há um limite em 25 processadores, qualquer processador que se adicione além desse valor, só atrasará o processamento. Figura 6: Influência do custo de paralelização. Assim, um tópico interessante é determinar qual a quantidade ótima de processadores para uma determinada tarefa. É claro que esse valor é fortemente influenciado pelo algoritmo e pela técnica de programação empregada. A arquitetura paralela também influencia muito. Por exemplo, algumas arquiteturas têm gargalos para a comunicação entre os processadores e outras penalizam muito os acessos à memória global. É claro que nem toda tarefa é indicada para ser executada em máquinas paralelas, como veremos no próximo tópico. Apesar do quanto promissor a computação paralela possa parecer, ela não é uma solução para todo o problema de processamento. Existem tarefas que são eminentemente seqüenciais e que não tiram proveito de um computador paralelo. Voltando ao nosso exemplo da construção de uma casa, apesar dela ser executada em paralelo, existe por detrás uma seqüência que deve ser obedecida. Nessa construção, não podemos fazer o telhado antes de termos as paredes prontas e também não podemos construir as paredes antes do alicerce. Assim, é comum que as tarefas a serem executadas possuam porções paralelizáveis e porções que precisam ser executadas de forma seqüencial. Note que um computador paralelo operando de forma seqüencial é um grande desperdício, pois enquanto um processador trabalha no trecho serial, todos os demais ficam ociosos. Abordando esse tema, Amdahl propôs uma expressão para esse problema, que ficou conhecida como Lei de Amdahl[3] e que está representada a seguir. A explicação é muito simples. Imaginemos uma tarefa que executada em uma máquina seqüencial gaste "T" segundos. Porém, quando preparada para execução em uma máquina paralela, ela tem uma porção que obrigatoriamente deve ser executada de forma serial. Digamos que "p" represente a porção serial, em conseqüência "(1-p)" representa a porção paralelizável. Quando executado em uma máquina paralela com N processadores, o tempo gasto será igual a "". Somente o trecho paralelizável tira partido dos "N" processadores. Assim o Ganho de Processamento é dado por: ou que é a forma consagrada da Lei de Amdahl. Deve-se notar que estamos ignorando os custos de sincronização e de troca de parâmetros entre os processadores. Vejamos em um gráfico o desempenho de alguns programas, segundo essa lei. A Figura 7 apresenta 4 casos. A curva em vermelho é a de uma tarefa 100% paralelizável, ou seja, p = 0. Nesse caso o aumento do número de processadores reflete linearmente no desempenho. A curva em verde ilustra o caso de p = 0,001 ou 0,1%, ou seja, apenas 0,1 % das tarefas não puderam ser paralelizadas. A curva em azul é para o caso onde 1% (p = 0,01) da tarefa precisa ser executada de forma serial. Nota-se uma grande queda de desempenho para grande quantidade de processadores. A última curva representa o caso de uma tarefa onde 10% (p = 0,1) precisam ser executadas de forma serial. Nota-se que há uma saturação, e que o aumento de processadores, por exemplo, de 50 para 100 processadores, pouca diferença traz para o desempenho. Devem ser ressaltados dois pontos importantes. O primeiro é que, exceto para o caso de p = 0, todos os demais casos irão apresentar saturação em algum ponto. Se p é pequeno, a saturação só ocorre com um elevado número de processadores. O segundo ponto é que, contrastando com a Figura 7, a Lei de Amdahl não prevê queda no desempenho, no pior caso, ele fica fixo em algum valor. Figura 7: Exemplos da Lei da Amdahl. Assim terminamos o este rápido estudo de processamento paralelo. Esperamos ter elucidado diversos conceitos básicos. Nas próximas partes dessa série de artigos ilustraremos nosso estudo abordando diversas arquiteturas paralelas propostas pelos gigantes de mercado para o próximo milênio. Continue lendo: Processadores para o próximo milênio - parte 3 [1] IEEE "Annals of the History of Computing" magazine, Volume 15, Number 4, 1993, page 28. [2] “Some Computer Organizations and their Effectiveness”, M. J. Flynn, IEEE Transactions on Computers, vol C-21, pp. 948-960, Setembro, 1972. [3] “Validity of the Single Processor Approach to Achieving Large Scale Computing Capabilities”, G. Amdahl, AFIPS Conference Proceeding, vol. 30, Abril, 1967, Thompson Books, Washington DC. [4] “Structured Computer Organization”, Andrew S. Tanenbaum, 4a Edição.

-

Finalmente, após o grande alarde do “Bug Y2K”, vamos ultrapassar a barreira do segundo milênio. Mas será que somos muito diferentes do homem de 2000 anos atrás? Não muito, o homem moderno, apesar de toda onda de informação, ainda lembra bastante seu antepassado, especialmente na adoração por datas, acontecimentos e cerimônias. Ao olharmos para trás, vimos que 2.000 anos formaram uma era. Quantas coisas nos separam daquele homem que não sabia medir o tempo, que acreditava que as estrelas eram candelabros de luzes e que a Terra era plana. O homem atual quebra os núcleos e transmuta os elementos, cria anti-matéria, manipula átomos, constrói máquinas inteligentes, envia naves além do Sistema Solar. Esta mesma sensação dual de mudança e não-mudança envolve-nos quando olhamos para trás em busca do nascimento da computação e, para a frente, querendo saber o que nos promete o próximo milênio. O presente artigo é o primeiro de uma série que irá explorar as realizações atuais e as especulações para o início do próximo milênio. Tentaremos apresentar um panorama diversificado, abordando não só as arquiteturas clássicas, mas também as evoluções que estão surgindo. Para tanto, não nos basta a experiência que temos com a família 80x86 para entendermos as novas arquiteturas, vamos precisar de alguns conceitos que serão abordados ao longo dos próximos artigos. Assim, vamos iniciar este artigo olhando para trás para apreciarmos o que aconteceu no passado e, em seguida, observaremos o mundo ao nosso redor e analisaremos o momento atual, para então abordamos as arquiteturas que serão as inovações para o próximo milênio. Finalmente, estudaremos em especial as arquiteturas de 64 bits da Intel (IA-64) e da AMD (x86-64). Qual foi o primeiro computador ? A resposta mais freqüente é o ábaco chinês, embora contestável por ele tratar-se de um instrumento auxiliar de cálculo. Acreditamos que o rótulo “computador no 1" deva ir para a calculadora mecânica de Blaise Pascal (homenageado com a linguagem Pascal), desenvolvida em 1642, que podia operar com números até 999.999.999. Em 1822, Charles Babbage desenvolveu a Máquina Diferencial (“Difference Engine”), que tinha uma arquitetura muito semelhante aos modernos processadores, apresentando CPU, memória e até linguagem de programação. A filha de Lord Byron, uma garota chamada Ada Byron[1], teve contato com esta máquina e acabou por se tornar a primeira programadora (em sua homenagem, temos hoje a linguagem ADA). Em 1833, Babbage projetou a Máquina Analítica (“Analytical Engine”), com capacidade de processamento muito superior, porém ela ficou limitada pela tecnologia mecânica daquela época. William Gibson, escritor, aproveita esse fato e nos conta uma interessante estória alternativa[2] de como seria o mundo se Babbage conseguisse construir sua máquina e o computador surgisse em pleno século XIX. Os século XX é marcado pelos grandes avanços. Gostaríamos de começar citando o romance “R.U.R.”[3], do tcheco Karel Capek, onde, em 1921, ele cria o termo “robot”, que na sua língua natal significa trabalhador. Sempre que falamos de robot, precisamos citar Isaac Asimov[4] e suas maravilhosas visões. Um marco importante neste século foi o ENIAC (do inglês “Electronic Numerical Integrator And Calculator”), ver Figura 1, projetado durante a Segunda Grande Guerra com a finalidade de calcular tiros de artilharia. Quando ele ficou pronto, em 1946, a guerra já havia acabado. Seu peso era de 30 t e consumia 140 kW. Um dos gênios que teve contato com esse projeto foi von Neumann, de quem falaremos mais adiante. Figura 1: ENIAC, sua programação era feita com fios ("hard wired"). Figura 2: Colossus, da Inglaterra. Sua programação também era feita com fios. Um outro grande projeto da época, anterior ao ENIAC e por isso pioneiro, foi o Colossus (Figura 2), desenvolvido na Inglaterra no período de 1939 a 1943 com a intenção de quebrar o código da máquina de criptografia alemã denominada Enigma, que gerava seqüências aleatórias com período de 1019 caracteres. Deste projeto, tomou parte Alan Turing, certamente um nome conhecido hoje em dia. Após a guerra, esse projeto foi descontinuado, mas permaneceu secreto até 1973. Dizem que, se esse projeto fosse publicado logo após a término da guerra, teríamos hoje uma grande indústria inglesa de computadores. Entramos em seguida na era da computação eletrônica, quando surgem os grandes computadores e, por detrás deles, as grandes empresas: IBM, Bourroughs, NCR, etc.. É a era de máquinas grandes, acessadas por uma multidão de terminais burros. Chegou-se a prever que no mundo haveria cinco grandes computadores, um para cada continente. Era a visão de homens simples perante máquinas maravilhosas e as vezes fatais, como conta Arthur Clark em "2001"[5]. Nas figuras a seguir vemos quatro marcos interessantes sobre esse passado. Para iniciar, falamos do termo “bug”, que sempre foi usado pelos engenheiros para indicar pequenas falhas em suas máquinas. Já em 1870, Thomas Edison falava de “bugs” em seus circuitos elétricos. Em 1947, os engenheiros que trabalhavam com o Harvard Mark I encontraram uma traça entre seus circuitos, prenderam-na no livro de registro e rotularam-na como o “primeiro bug” encontrado, como vemos na Figura 3. E como eles se tornariam comum! Na Figura 4 está o computador IAS, de 1952, que foi construído segundo orientação de von Newmann e muito influenciou o projeto do IBM 701, o primeiro computador eletrônico comercializado pela IBM. Temos ainda, na Figura 5, o UNIVAC, projetado pelos idealizadores do ENIAC. Finalmente, a Figura 6 mostra o PDP-8, primeiro computador com preço acessível, tendo sido uma máquina da série PDP onde Ken Thompson e Dennis Ritchie desenvolveram o UNIX. Figura 3: O primeiro "bug", 1947. Figura 4: Computador IAS, 1952. Figura 5: Modelo do UNIVAC, 1954. Figura 6: Minicomputador PDP-8, 1965. Essa visão de grandes máquinas, inalcançáveis para os pobres mortais, domina até 1971, quando surge o primeiro microprocessador, o Intel 4004. No início, não chamou muita atenção, mas paulatinamente foram surgindo outros processadores e, na esteira desses processadores, companhias que fabricavam pequenos computadores. O computador começava a aproximar-se do homem comum. Surgia assim o mercado dos microcomputadores. Nele, destacaram-se empresas que tropeçaram com o sucesso, que se tornaram gigantes e que passaram a ameaçar a posição de companhias do porte da HP e IBM. Essa história é contada de forma divertida por Robert Cringely em seu livro “Accidental Empires”[6]. Já mais voltada para o projeto de CPUs é a abordagem de Tracy Kidder em seu livro “The Soul of a New Machine”[7]. Já na área dos microcomputadores, perguntamo-nos: qual foi o primeiro ? Em 1975 a Revista “Popular Electronics” apresentou o projeto e anunciou a venda do “kit” do primeiro microcomputador. Era o Altair 8800, baseado no microprocessador 8008 da Intel, cuja foto está na Figura 7. O nome Altair é uma homenagem ao planeta onde se passa o filme “O Planeta Proibido” (1956) , onde aparece um robot (“Robbie”) cuja imagem ficaria famosa (Figura 8). Foi também para esse microcomputador que a dupla Paul Allen e Bill Gates vendeu um de seus primeiros produtos: um interpretador Basic. Figura 7: Altair 8008, o primeiro microcomputador. Figura 8: Cartaz do filme O Planeta Proibido, que inspirou o nome Altair. Outro fato marcante dessa época é o projeto da Xerox, no centro de pesquisas em Palo Alto, onde se desenvolveram vários conceitos de informática, inovadores para a época. Desse projeto surgiram o mouse, os ícones, as janelas e ainda computadores ligados em redes e as mensagens eletrônicas. Eram conceitos tão revolucionários que a alta direção da Xerox não soube aproveitá-los, mas Steve Jobs soube e colocou-os todos no Macintosh. Há quase vinte anos, em 1981, a IBM lançava seu microcomputador provocando um verdadeiro terremoto no mercado e terminando por polarizá-lo entre o IBM PC e o Macintosh da Apple. Na verdade, o primeiro microcomputador da IBM, o IBM 5100, lançado em 1975, foi um fracasso[8]. Nesses últimos vinte anos, experimentamos uma evolução de tirar o fôlego. Um PC equipado com um Pentium III é mais barato e duas mil vezes mais rápido que o PC XT original, isto sem falarmos dos recursos de vídeo 3D, som, DVD e Internet. A resposta é: não vamos parar. É claro que a evolução vai continuar, mas a atual arquitetura dos microcomputadores deverá mudar bastante, pois a concorrência está cada dia mai acirrada. Vejamos, por exemplo, o caso das estações de trabalho, antigamente tão superiores aos microcomputadores e que hoje disputam um mesmo mercado. Ao mesmo tempo que os microprocessadores caminham em direção às arquiteturas de 64 bits, surgem outros como processadores como os dedicados à Internet, os processadores para os roteadores e chaveadores das redes de alta velocidade e até processadores RISC com arquitetura passível de ser alterada pelo usuário. Com essa rápida resenha da história, particularizada no final para os microcomputadores, terminamos a primeira parte deste artigo. Vemos que muita coisa mudou, mas nem tanto, pois os computadores que usamos em casa seguem a mesma arquitetura proposta por von Newmann, ainda na década de 50. Assim, na continuação, abordaremos os postulados de von Newmann e estudaremos alguns conceitos de processamento paralelo, pois eles são fundamentais para entendermos os supercomputadores atuais e os que estão sendo projetados para o próximo milênio. Continue lendo: Processadores para o próximo milênio - parte 2 Livros [1] "Ada, the Enchantress of Numbers", Betty A. Toole (Editor). [2] "The Difference Engine", William Gibson. [3] "De Júlio Verne aos Astronautas", Coleção Argonauta, Número 100. [4] "Eu, Robô", Issac Asimov. [5] "HAL’s Legacy", David G. Stork (Editor). [6] "Accidental Empires", Robert X. Cringely. [7] "The Soul of a New Machine", Tracy Kidder. [8] "History of Computing", Mark Greenia. Sites Ada: http://www.agnesscott.edu/lriddle/women/love.htm Altair IV: http://neptune.spaceports.com/~slacker/altair4/ ENIAC: http://americanhistory.si.edu/csr/comphist/pr1.pdf e http://americanhistory.si.edu/csr/comphist/pr4.pdf. Colossus: http://www.cranfield.ac.uk/ccc/bpark/colossus.htm Diversos: http://www.cs.yale.edu/homes/tap/photo_gallery.html Histórico: http://americanhistory.si.edu/csr/comphist/

-