Índice

Índice

- Introdução

- RAM Dinâmica vs. RAM Estática

- História do Cache de Memória nos PCs

- O Cache de Memória

- Cache de Memória L2 nos Processadores Multi-Núcleos

- Como o Cache de Memória Funciona

- Organização do Cache de Memória

- Cache Associativo por Grupos de n-vias

- Configuração do Cache de Memória nos Processadores Atuais

O Cache de Memória

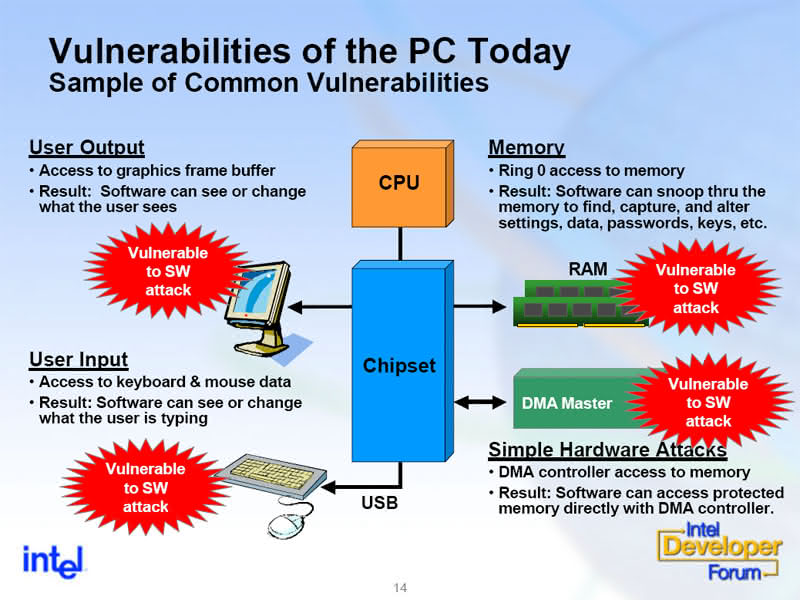

Na Figura 2 você pode ver um diagrama em blocos básico de um processador de núcleo único. É claro que o diagrama em blocos varia dependendo do processador e você pode ler nossos tutoriais para cada linha de processadores para dar uma olhada em seus diagramas em blocos (Por Dentro da Arquitetura do Pentium 4, Por Dentro da Microarquitetura Core e Por Dentro da Arquitetura AMD64).

Figura 2: Diagrama em bloco básico de um processador.

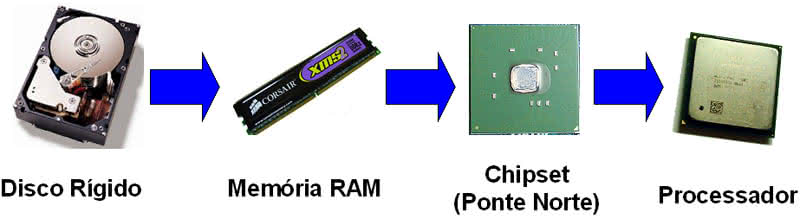

A linha pontilhada na Figura 2 representa o corpo do processador, já que a memória RAM está localizada fora do processador. O caminho de dados entre a memória RAM e processador tem geralmente largura de 64 bits (ou de 128 bits, quando a configuração de dois canais – “dual channel” – é usada), rodando ao clock da memória ou ao clock externo do processador (ou clock do barramento da memória, no caso dos processadores da AMD), o que for mais baixo. Nós já mostramos como calcular a taxa de transferência da memória na primeira página deste tutorial.

Todos os circuitos dentro da caixa pontilhada rodam no clock interno do processador. Dependendo do processador, algumas de suas partes internas podem até mesmo rodar a uma taxa de clock mais alta. Além disso, o caminho de dados entre as unidades do processador pode ser mais largo, isto é, transferir mais bits por pulso de clock do que 64 ou 128. Por exemplo, o caminho de dados entre a memória cache L2 e o cache L1 de instruções em processadores modernos tem normalmente largura de 256 bits. Quanto maior o número de bits transferidos por pulso de clock, mais rápida a transferência será feita (em outras palavras, a taxa de transferência será mais alta).

Em resumo, todos os processadores modernos têm três caches de memória: o L2, que é o maior e pode ser encontrado entre a memória RAM e o cache L1 de instruções, que armazena tanto dados quanto instruções; o cache L1 de instruções, que é usado para armazenar instruções que serão executadas pelo o processador; e o cache L1 de dados, que é usado para armazenar dados que serão escritos de volta na memória.

L1 e L2 significam “nível 1” (Level 1) e “nível 2” (“Level 2”), respectivamente, e referem-se à distância em que se encontram do núcleo do processador (unidade de execução). Uma dúvida comum é porque ter três memórias cache distintas (cache L1 de dados, cache L1 de instruções e L2).

Fazer com que a latência das memórias estáticas seja igual a zero é um enorme desafio, especialmente com os processadores trabalhando com clocks muito altos. Como fabricar memórias estáticas com latência igual a zero é muito difícil, o fabricante usa este tipo de memória apenas no cache de memória L1. O cache de memória L2 usa uma RAM estática que não é tão rápida quanto à usada no cache L1, já que ela tem alguma latência, o que faz com que o seu acesso seja um pouco mais lento do que o acesso ao do cache de memória L1.

Preste atenção na Figura 2 e você verá que o cache L1 de instruções funciona como um cache de entrada, enquanto que o cache L1 de dados funciona como um cache de saída. O cache L1 de instruções – que é normalmente menor do que o cache L2 – é particularmente eficiente quando o programa iniciar um laço de repetição (loop), já que as instruções necessárias já estarão próximas da unidade de busca.

Isto é raramente mencionado, mas o cache L1 de instruções é também usado para armazenar outros dados além das instruções a serem decodificadas. Dependendo do processador ele pode ser ainda usado para armazenar alguns dados de pré-decodificação e informações de desvio (em resumo, dados de controle que aumentarão a velocidade do processo de decodificação) e às vezes o cache L1 de instruções é maior do que o anunciado, pois o fabricante não adiciona o espaço extra disponível para o armazenamento dessas informações adicionais.

Na página de especificações de um processador o cache L1 pode ser encontrado com diferentes tipos de representação. Alguns fabricantes listam as memórias cache L1 separadamente (algumas vezes chamando o cache de instrução de “I” e o cache de dados de “D”), alguns acrescentam a soma dos dois e escrevem “separados” – logo “128 KB, separados” significa cache de instruções de 64 KB e cache de dados de 64 KB –, e alguns simplesmente somam os dois e você tem que adivinhar que o número é o total e que você deve dividi-lo por dois para saber a capacidade de cada cache. A exceção, entretanto, fica por conta dos processadores baseados na microarquitetura Netburst, como os processadores Pentium 4, Pentium D e o Xeon e o Celeron baseados no Pentium 4.

Os processadores baseados na microarquitetura NetBurst não possuem cache L1 de instruções. Em vez disto eles possuem um cache de rastreamento de execução, que é um cache localizado entre a unidade de decodificação e a unidade de execução. Portanto, o cache L1 de instruções está lá, mas com nome e lugar diferentes. Estamos falando isso porque esse é um erro muito comum, pensar que processadores Pentium 4 não possuem cache L1 de instruções. Quando comparam o Pentium 4 com outros processadores, algumas pessoas acham que seu cache L1 é muito menor, porque estão contando apenas o cache de dados L1 de 8 KB. O cache de rastreamento de execução dos processadores baseados na microarquitetura NeBurst é de 150 KB e deve ser levado em conta, é claro.

Respostas recomendadas

Crie uma conta ou entre para comentar

Você precisa ser um usuário para fazer um comentário

Criar uma conta

Crie uma nova conta em nossa comunidade. É fácil!

Crie uma nova contaEntrar

Já tem uma conta? Faça o login.

Entrar agora