Decodificador CISC/RISC

Desde da geração anterior (6ª geração), os processadores da Intel utilizam uma arquitetura híbrida CISC/RISC. O processador deve aceitar instruções CISC, também conhecidas como instruções x86, já que todos os programas disponíveis hoje são escritos usando este tipo de instruções. Um processador inteiramente RISC não poderia ser criado para ser usado nos PCs porque ele não pode rodar programas que temos disponíveis hoje, como Windows e Office.

Portanto, a solução usada por todos os processadores disponíveis no mercado hoje, tanto da Intel quanto da AMD, é usar um decodificador CISC/RISC. O processador trabalha internamente executando instruções RISC, mas aceita apenas instruções CISC x86.

Instruções CISC x86 são conhecidas como “instruções”, enquanto que as instruções RISC são conhecidas como “microinstruções” ou “µops”.

Essas microinstruções RISC, no entanto, não podem ser acessadas diretamente e, portanto, não poderíamos criar programas baseados nessas instruções e enviá-las para as unidades de execução passando por cima do decodificador de instruções. Além disso, cada processador possui seu próprio conjunto de instruções RISC, que não são divulgadas pelo fabricante e são incompatíveis com as microinstruções de outros processadores. Por exemplo, as microinstruções do Pentium III são diferentes das microinstruções do Pentium 4, que são diferentes das microinstruções do Athlon 64.

Dependendo da complexidade da instrução x86 ela pode ser convertida em várias microinstruções RISC.

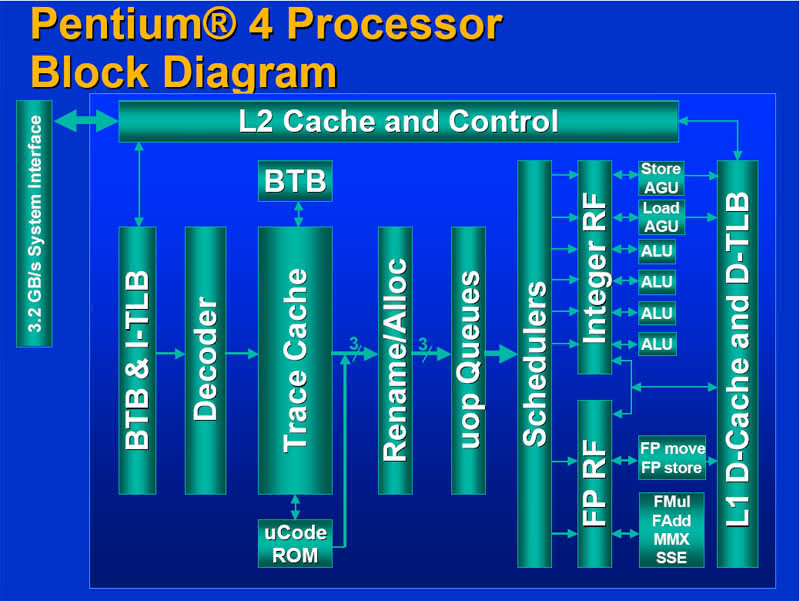

O decodificador do Pentium 4 pode decodificar uma instrução x86 em até quatro microinstruções RISC por pulso de clock. As instruções mais complexas e que precisam ser convertidas em mais do que quatro microinstruções na verdade não são convertidas: é consultada uma memória ROM (“ROM Microcódigo” na Figura 3) contendo uma lista de microinstruções para a conversão daquela instrução. Essa memória ROM é chamada de Sequenciador de Instruções de Microcódigo (MIS, Microcode Instruction Sequencer).

Como falamos anteriormente, após serem decodificadas as microinstruções são enviadas para o cache de microinstruções e de lá seguem para uma fila de microinstruções. O cache de microinstruções pode colocar até três microinstruções na fila por pulso de clock, apesar da Intel não divulgar o tamanho desta fila.

De lá, as instruções vão para o Alocador e para a unidade de Renomeamento de Registradores. A fila pode também entregar até três microinstruções por pulso de clock para o Alocador.

Respostas recomendadas

Não há comentários para mostrar.

Crie uma conta ou entre para comentar

Você precisa ser um usuário para fazer um comentário

Criar uma conta

Crie uma nova conta em nossa comunidade. É fácil!

Crie uma nova contaEntrar

Já tem uma conta? Faça o login.

Entrar agora