Introdução

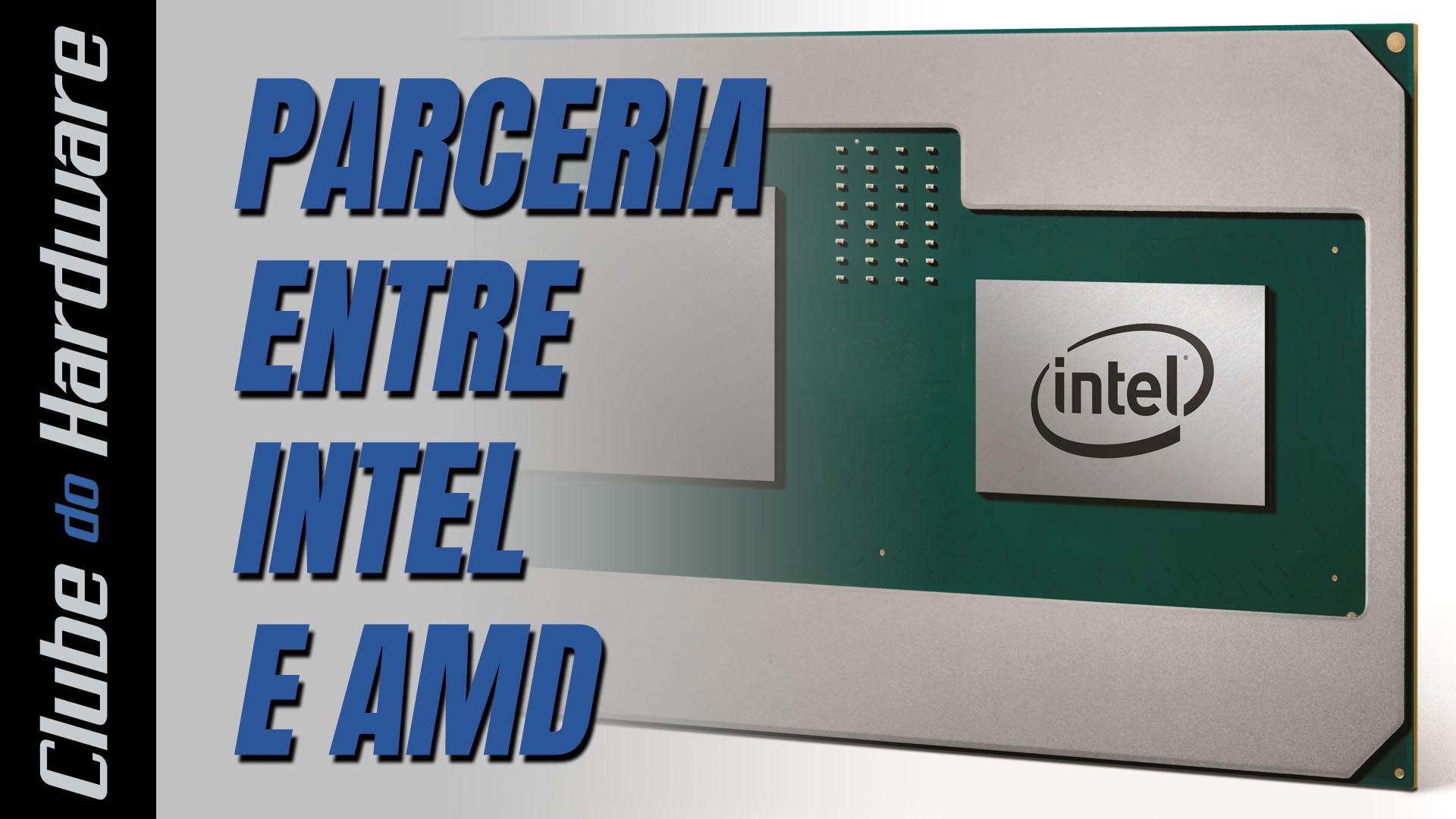

A microarquitetura Broadwell, usada nos processadores Core i de quinta geração e também em outras linhas de processadores da Intel (Core M e futuros modelos do Xeon), adiciona pequenas melhorias à microarquitetura anterior do fabricante, a Haswell. Sua principal novidade é o uso de um novo processo de fabricação, de 14 nm (processadores Haswell utilizam processo de 22 nm).

É importante entender que a Intel utiliza um cronograma chamado “tique-taque” (“tick-tock”, em inglês), onde o “tique” representa uma microarquitetura utilizando um novo processo de fabricação. Esta microarquitetura não traz grandes mudanças em relação à microarquitetura anterior, sendo feitos apenas pequenos ajustes e melhorias. Já o “taque” representa uma microarquitetura completamente nova, utilizando o mesmo processo de fabricação da microarquitetura anterior. A ideia é utilizar uma microarquitetura completamente nova somente após o fabricante dominar completamente o novo processo de fabricação.

Dentro desse cronograma, a microarquitetura Broadwell é “tique” e, logo, não traz nenhuma mudança estrutural severa em relação à microarquitetura Haswell. Portanto, para compreender a microarquitetura Broadwell e tirar maior proveito deste tutorial, leia o nosso tutorial “Por dentro da microarquitetura Intel Haswell”.

Para computadores de mesa, os processadores Core i de quinta geração continuarão usando o soquete LGA1150, introduzido com os processadores Core i de quarta geração (Haswell).

Como é óbvio de se supor, várias melhorias foram feitas para aumentar o desempenho, diminuir o consumo elétrico e diminuir a dissipação térmica.

As principais novidades da microarquitetura Broadwell em relação à microarquitetura Haswell são as seguintes:

- Três novas instruções de criptografia e segurança

- Novo modo SMAP (Supervisor Mode Access Protection, proteção de acesso do modo supervisor), que expande o modo SMEP introduzido na microarquitetura Ivy Bridge para impedir código supervisor de bisbilhotar dados em páginas de memória do usuário

- Novo estado de economia de energia C7+

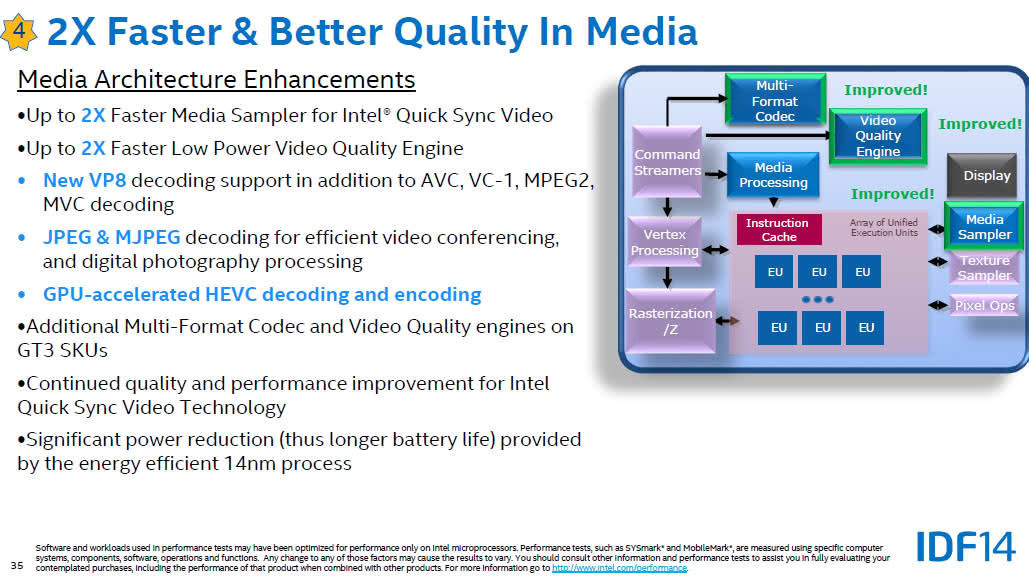

- Motor de vídeo suportando decodificação dos formatos VP8, HVEC e JPEG por hardware, além de codificador no formato HVEC

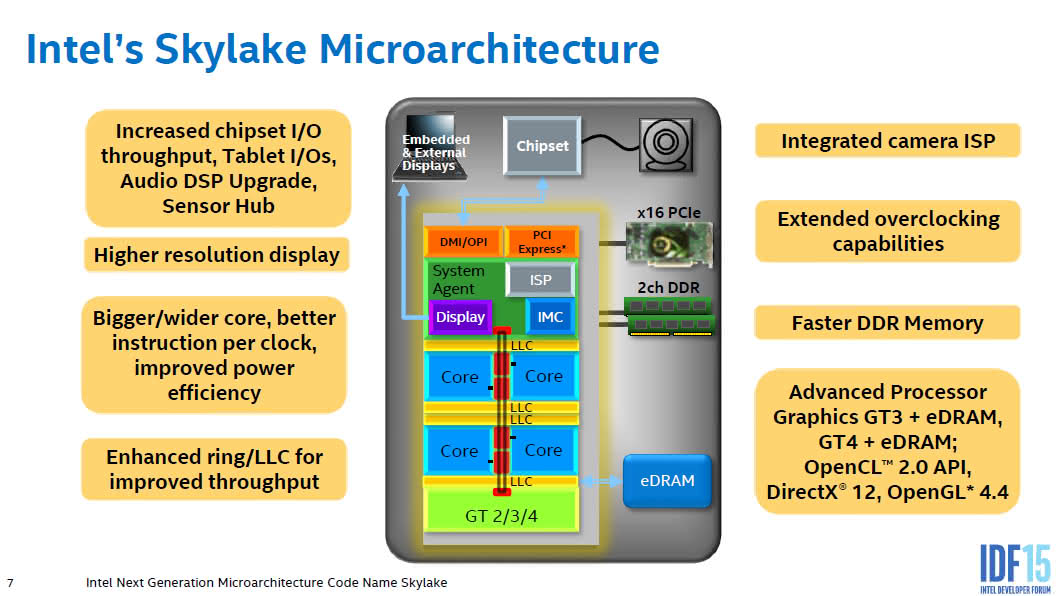

- Motor gráfico DirectX 11.2 e OpenGL 4.3

- Melhoria na técnica de GPGPU, com a adoção da interface de programação OpenCL 2.0

- Aumento de dois processadores por módulo no motor gráfico

- Novo sistema de “debug” chamado “Intel Processor Trace”, voltado a desenvolvedores de software

- Adoção da técnica de “throtle” para o chipset nos modelos com chipset integrado (SoC), de forma a diminuir o consumo e dissipação

- Melhorias no consumo elétrico

- Melhorias na dissipação térmica

- Melhorias na tecnologia de virtualização (menor tempo de transição)

- Agendador da unidade de execução fora de ordem aumentado de 60 para 64 entradas

- Buffer de tradução de endereços (TBL) aumentado

- Diminuição na latência no envio de microinstruções a serem processadas

- Melhorias diversas em várias áreas para aumentar o desempenho

Vamos agora falar de algumas melhorias específicas que vale a pena serem explicadas em mais detalhes.

Respostas recomendadas

Crie uma conta ou entre para comentar

Você precisa ser um usuário para fazer um comentário

Criar uma conta

Crie uma nova conta em nossa comunidade. É fácil!

Crie uma nova contaEntrar

Já tem uma conta? Faça o login.

Entrar agora