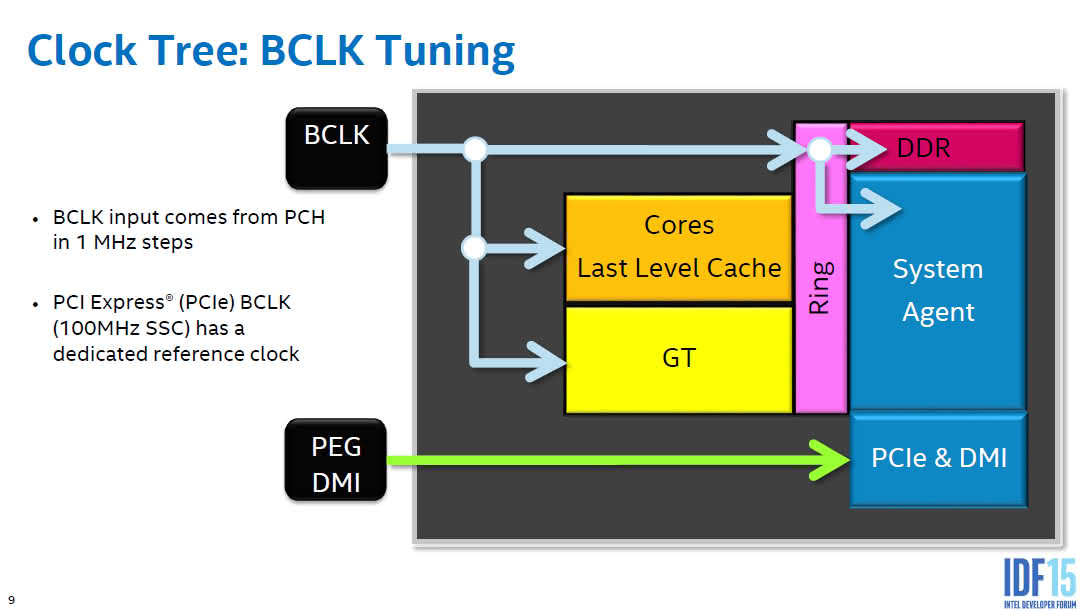

Mudanças na microarquitetura

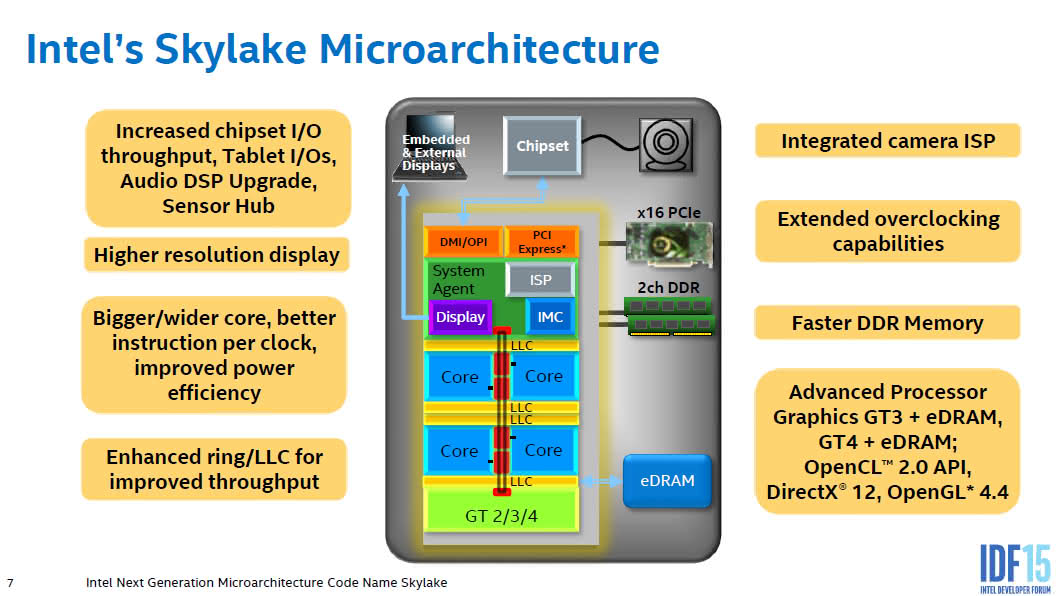

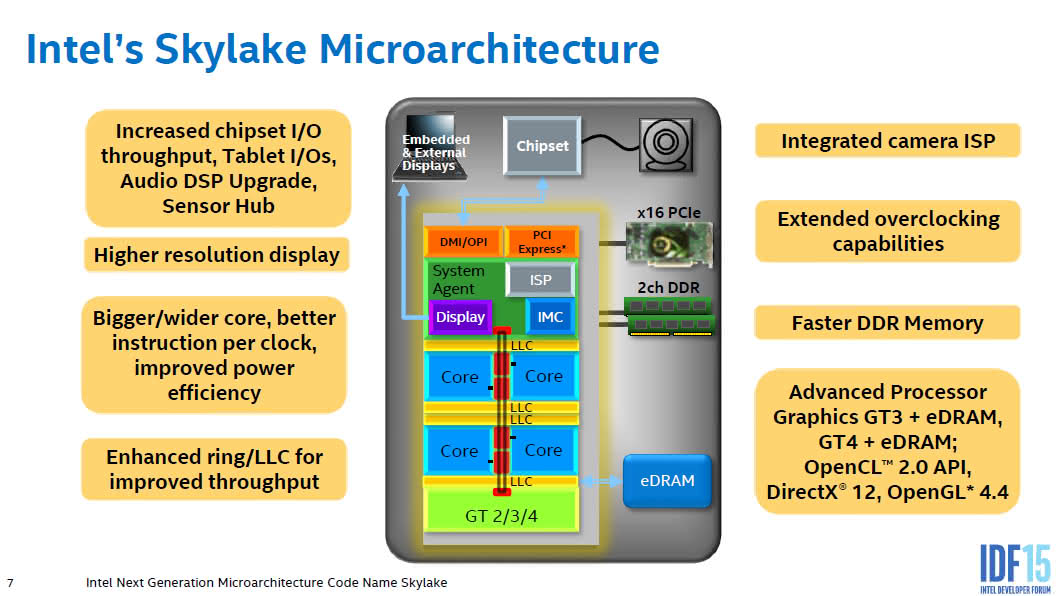

A microarquitetura Skylake utiliza a mesma arquitetura em anel que foi originalmente introduzida na microarquitetura Sandy Bridge (usada nos processadores Core i de segunda geração) e usada pelas microarquiteturas seguintes. Em relação à microarquitetura Broadwell, dois elementos foram adicionados, como você pode conferir na Figura 1: um processador integrado de sinais para câmeras (ISP, Integrated Signal Processor), suportando até quatro câmeras totais e duas simultâneas com resolução máxima de 13 megapixels e 1080p a 60 quadros por segundo ou 4K a 30 quadros por segundo (ver Figura 2), e a localização da memória eDRAM opcional disponível em alguns modelos (compare as Figuras 3 e 4).

Figura 1: diagrama em blocos da microarquitetura Skylake (alto nível)

Figura 2: detalhes do processador integrado de sinais para câmeras

A partir da microarquitetura Haswell, o processador já podia ter uma memória eDRAM nos modelos com o motor gráfico “GT3e” (isto é, Iris Pro 5200 nos processadores Haswell e Iris Pro 6200 nos processadores Broadwell), mas ela era usada apenas pelo motor gráfico do processador e seu acesso passava obrigatoriamente pelo cache de memória L3. Ver Figura 3.

Figura 3: localização da memória eDRAM opcional nos processadores Haswell e Broadwell

Já nos processadores Skylake, a localização dessa memória eDRAM opcional foi modificada, permitindo que ela seja usada em qualquer tipo de acesso à memória (RAM) e não somente pelo motor gráfico. Ver Figura 4. Esta memória eDRAM está disponível nos modelos Skylake com motor gráfico “GT3e” (Iris 540 e 550) e “GT4e” (Iris Pro 580).

Figura 4: localização da memória eDRAM opcional nos processadores Skylake

A microarquitetura Skylake utiliza o mesmo mecanismo de funcionamento em relação às microarquiteturas anteriores, mas com um aumento na capacidade de transferir e armazenar dados, o que aumenta o desempenho. A Figura 5 compara os principais pontos que foram melhorados em relação às microarquiteturas Haswell (a Broadwell neste ponto é idêntica à Haswell) e Sandy Bridge (a Haswell neste ponto é idêntica à Sandy Bridge).

Figura 5: principais mudanças na microarquitetura Skylake (baixo nível)

Tradução da Figura 5:

- Out-of-order window: janela do mecanismo de execução fora de ordem

- In-flight loads: carregamentos de memória em tempo real

- In-flight stores: armazenamento em memória em tempo real

- Scheduler entries: entradas no agendador

- Integer register file: número de registradores de inteiros presentes na unidade de renomemento de registradores

- FP register file: número de registradores de ponto flutuante presentes na unidade de renomemento de registradores

- Allocation queue: fila de alocação

Para um entendimento mais aprofundado no que significa cada um desses pontos, o ideal seria você ler o nosso livro “Hardware”, em particular o Capítulo 15. Porém, se você seguir a sequência de leitura abaixo de nossos tutoriais você será capaz de compreender o que significa e a importância de cada um desses itens:

- Por dentro da arquitetura do Pentium M

- Por dentro da microarquitetura Intel Core

- Por dentro da microarquitetura Intel Nehalem, página “Aprimoramentos do pipeline do processador”

- Por dentro da microarquitetura Intel Sandy Bridge, página “Aprimoramentos do pipeline do processador”

- Por dentro da microarquitetura Haswell, página “Novas portas de despacho e unidades de execução”

Respostas recomendadas

Não há comentários para mostrar.

Crie uma conta ou entre para comentar

Você precisa ser um usuário para fazer um comentário

Criar uma conta

Crie uma nova conta em nossa comunidade. É fácil!

Crie uma nova contaEntrar

Já tem uma conta? Faça o login.

Entrar agora