Registradores de Controle

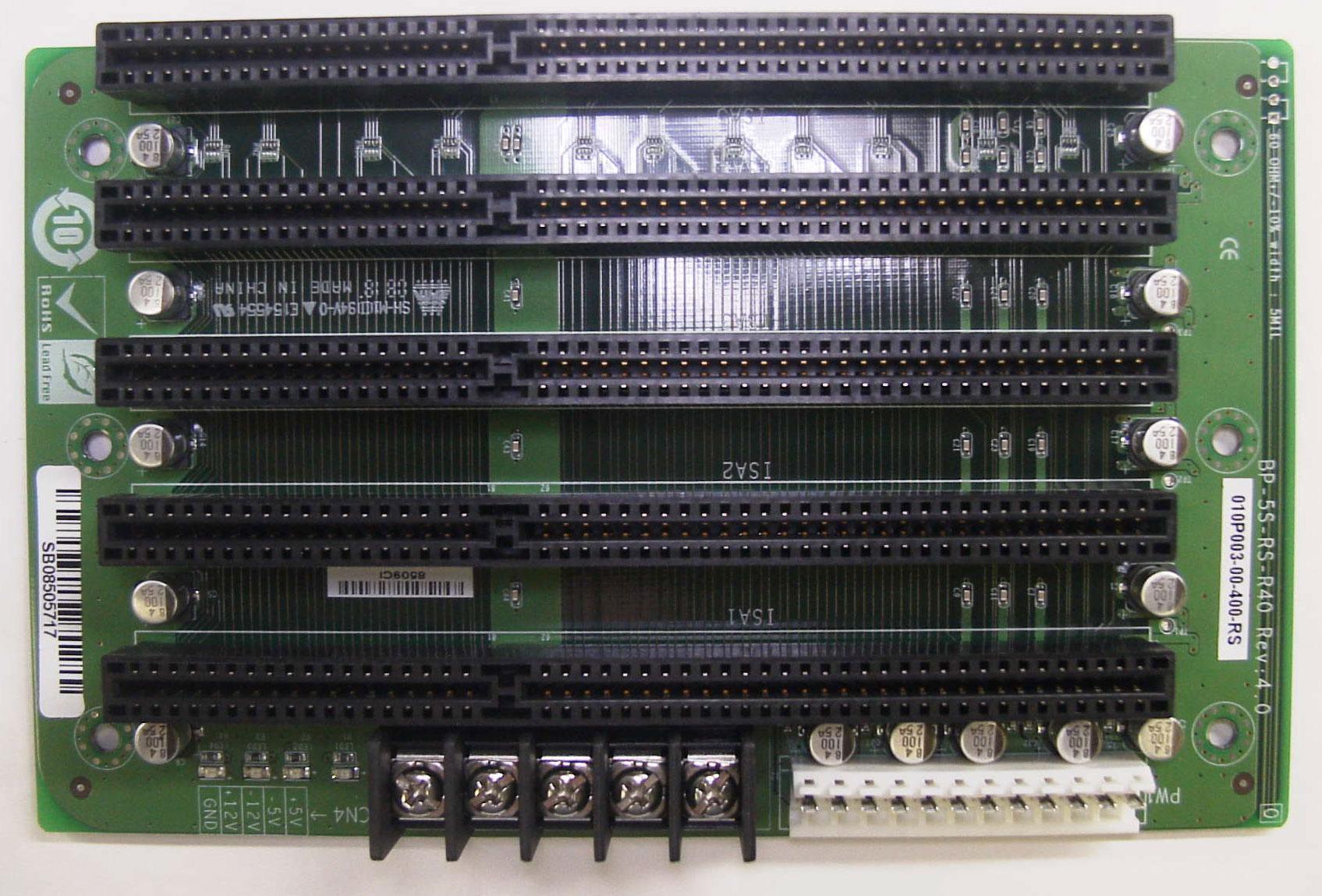

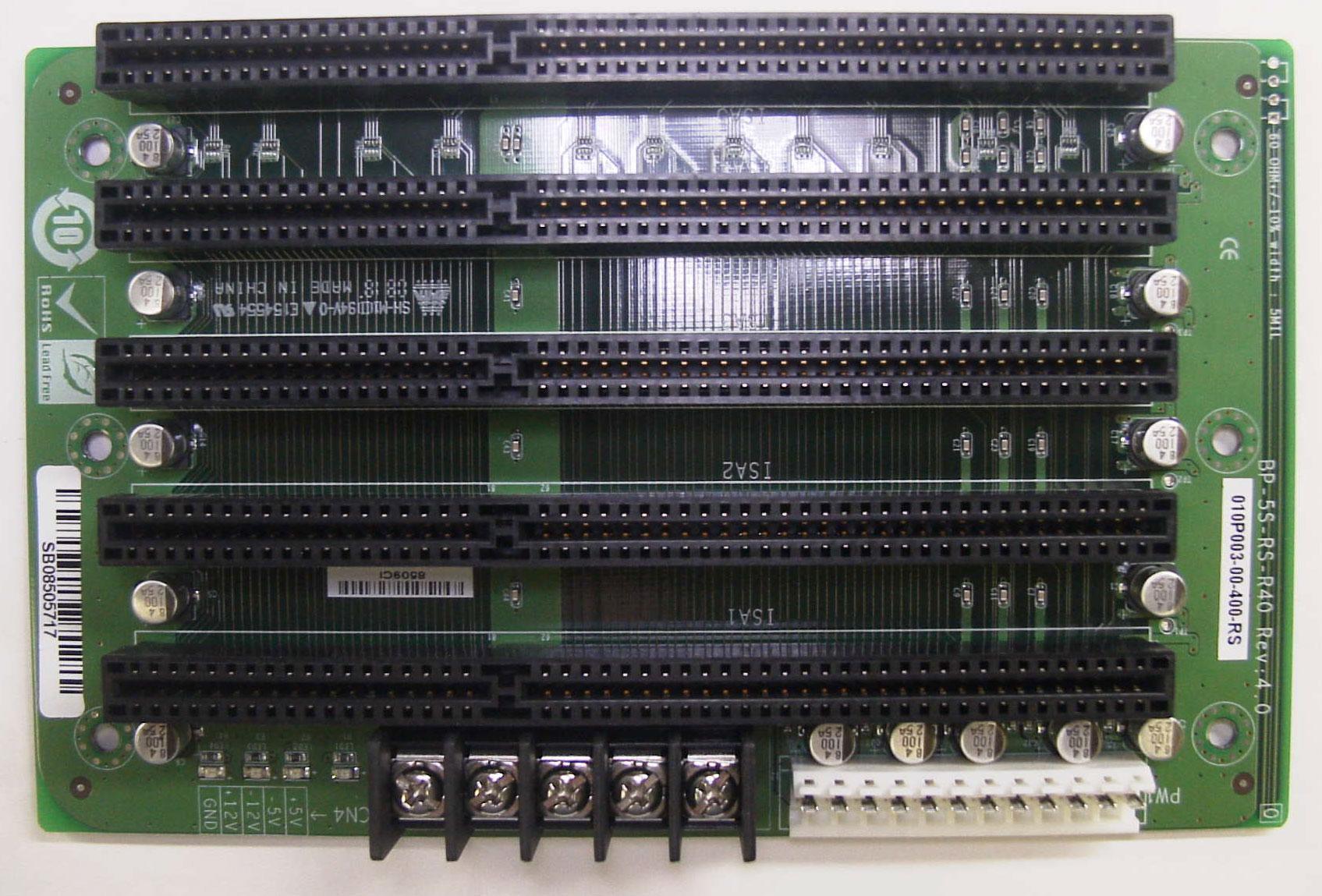

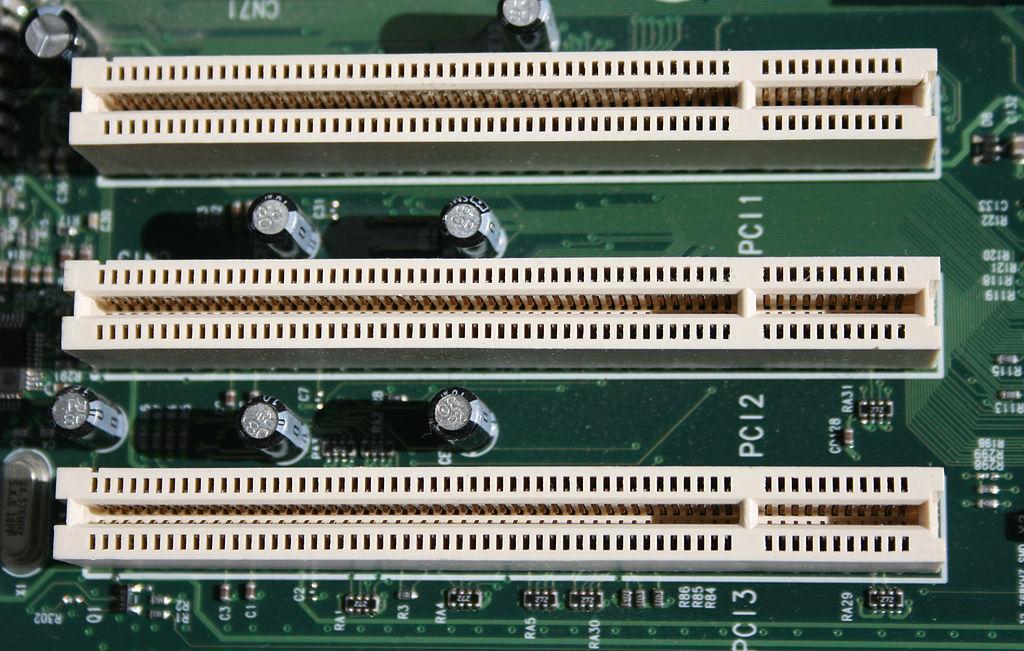

Todo projeto ISA plug and play deve implementar 8 registradores para o controle de configuração do adaptador físico (conectado ao slot) e alguns outros para cada dispositivo lógico presente (ex: porta serial, interface de disco, porta paralela, etc. - cada dispositivo pode exigir seus próprios recursos). Ver Figura 1.

Para selecionar qual registrador será acessado num determinado instante, escreve-se um offset (de acordo com a Figura 1) no registrador de endereços (279h). Decodifica-se o valor escrito, visando a condicionar a habilitação do registrador selecionado a um ciclo de I/O para o endereço do registrador de escrita (A79h) ou para o registrador de leitura (programável), e à condição de não se estar no estado de Espera por Chave. O circuito 2 realiza esta função. Notar que os sinais Y00h a Y07h são os offsets já decodificados.

| offset | registrador | presença |

| 00h | Reg. de Endereço de Leitura | um por placa |

| 01h | Reg. de Seqüência de Isolamento | um por placa |

| 02h | Reg. de Controle de Configuração | um por placa |

| 03h | WAKE | um por placa |

| 04h | Reg. Dados dos Recursos | um por placa |

| 05h | Reg. de Estado | um por placa |

| 06h | CSN | um por placa |

| 07h | Reg. Seleção do Dispositivo | um por placa |

| 30h | Ativação | dispositivo |

| 31h | I/O Check | dispositivo |

| 40h a 5Ch | Descritores de Memória | dispositivo |

| 60h e 61h | bloco de I/O | dispositivo |

| 62h e 63h | boco de I/O | dispositivo |

| 64h e 65h | bloco de I/O | dispositivo |

| 66h e 67h | bloco de I/O | dispositivo |

| 68h e 69h | bloco de I/O | dispositivo |

| 6Ah e 6Bh | bloco de I/O | dispositivo |

| 6Ch e 6Dh | bloco de I/O | dispositivo |

| 6Eh e 6Fh | bloco de I/O | dispositivo |

| 70h e 71h | canal de interrupção | dispositivo |

| 72h e 73h | canal de interrupção | dispositivo |

| 74h | canal de DMA | dispositivo |

| 75h | canal de DMA | dispositivo |

| 76h a A8h | blocos de memória | dispositivo |

Figura 1: Mapeamento dos registradores de configuração de uma placa ISA plug and play.

Circuito 2: Faz a seleção adequada do registrador de controle.

O registrador de Endereço de Leitura (offset 00h) é programado pelo software plug and play e define, dentre 203h e 3FFh, qual o endereço atribuído para o registrador de leitura. A regra é simples: o bit 7 escrito corresponde ao bit 9 do registrador de leitura, o bit 6 ao bit 8 e assim por diante. Os dois bits menos significativos foram arbitrados iguais a 1. O circuito 3 implementa este registrador. A seguinte seqüência de código programa o registrador de leitura para o endereço 203h:

mov dx, 279h ;seleciona reg. de endereços mov al, 0h ;seleciona offset 00h out dx, al ;realiza ciclo de I/O mov dx, A79h ;seleciona reg. de escrita mov al, 80h ;programa pela regra 203h out dx, al ;realiza ciclo de I/O

Circuito 3: Controla leituras aos registradores de configuração.

O registrador de Seqüência de Isolamento (offset 01h) é responsável por colocar 55h ou AAh no barramento, isto quando o adaptador estiver participando da seqüência de isolamento.

O registrador de Controle de Configuração (offset 02h), conforme ilustrado na Figura 2 e implementado no circuito 4, é utilizado para zerar o número de seleção de todas as placas (CSN) ou o de todos os dispositivos lógicos e também para colocar todas as placas no estado Espera por Chave, para que fiquem operacionais.

Figura 2: Mapeamento do registrador de Controle de Configuração.

Circuito 4: Implementação do registrador de controle de configuração.

Os offsets relativos a WAKE e CSN (03h e 06h) são gerenciados de forma que, quando WAKE=CSN (CSN é programado durante a seqüência de isolamento), o adaptador fica selecionado como foco de entrada para determinados acessos. Um valor CSN=0 é inválido, devendo ser interpretado como se CSN¹WAKE, pois a placa requer uma seqüência de isolamento. O circuito 5 implementa a comparação CSN=WAKE.

O registrador de Dados dos Recursos (offset 04h) permite que se obtenham dados do fabricante, número de série, identificadores de dispositivos lógicos e descritores que informam que recursos estes exigem.

O registrador de Estado (offset 05h) informa se o adaptador está pronto para ter seu registrador de Dados dos Recursos acessado.

Circuito 5: Verifica se o adaptador está selecionado, ou seja, se está no modo de Configuração.

O registrador de Seleção do Dispositivo (offset 07h), em placas com mais de um dispositivo lógico implementado, é comparado com o identificador do dispositivo para, no máximo, permitir que um dos dispositivos lógicos seja o foco de entrada para a programação de recursos. O circuito 6 realiza tal comparação. A partir deste ponto, supõem-se gerados sinais Y30h a YFFh, condicionados ao casamento do dispositivo lógico.

A Figura 3 (circuito 7) sugere a implementação de uma região de 8 endereços consecutivos de I/O, programável pelos offsets 60h e 61h. Notar que os bits A8 a A15, que compõem os endereços da região de I/O são escritos e lidos com offset 60h, e que os bits A3 a A7 são acessados pleo offset 61h. Observar que uma leitura deste offset retorna os 3 bits menos significativos iguais a zero. Desta forma, para que o software plug and play saiba o tamanho da região de I/O a alocar, basta escrever FFh nos offsets 60h e 61h. Em seguida, fazer uma leitura dos mesmos. O número de bits iguais a zero está associado ao tamanho da região a alocar. No exemplo da Figura 3, são lidos três bits nulos, o que informa que são 8 (23) endereços de I/O necessários. A programação de blocos de memória é parecida com a de blocos de I/O, e, por isso, não será detalhada.

Circuito 6: Checa o casamento do dispositivo selecionado com o dispositivo lógico.

Figura 3: Circuito para a programação de uma região de 8 endereços de I/O.

A Figura 4 (circuito 8) mostra como são programados os recursos de interrupção (offsets 70h e 71h). Pelo offset 70h, é passado o valor da IRQ alocada, que é decodificado para permitir que o pedido de interrupção seja conectado eletricamente ao barramento. O offset 71h é responsável por informar o tipo de ativação elétrica. No caso da Figura 4, optou-se por uma interrupção ativada por nível alto.

O circuito 8 (para programar um canal de DMA) lembra a Figura 3. Contudo, cada sinal gerado pelo decodificador controla duas conexões elétricas: a do pedido de DMA e a do reconhecimento do pedido.

Reparar que os circuitos 8 e 9 são alimentados pelo sinal HAB BARR, que condiciona todas as conexões de saída para o barramento e é gerado pelo circuito 1.

Figura 4: Circuito para receber um valor de IRQ e conectar o pedido de interrupção ao barramento.

Circuito 9: Programa um canal de DMA.

Respostas recomendadas

Não há comentários para mostrar.

Crie uma conta ou entre para comentar

Você precisa ser um usuário para fazer um comentário

Criar uma conta

Crie uma nova conta em nossa comunidade. É fácil!

Crie uma nova contaEntrar

Já tem uma conta? Faça o login.

Entrar agora