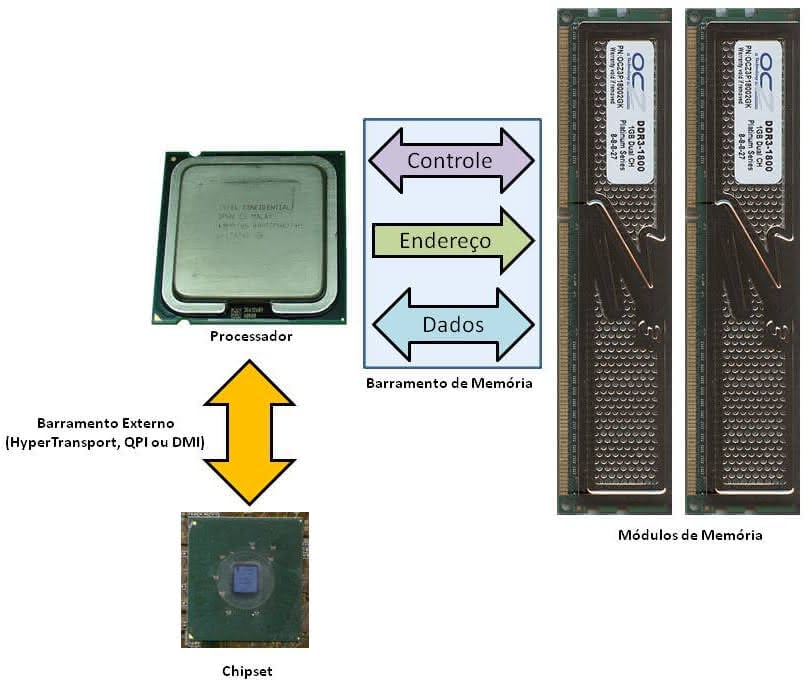

RAS to CAS Delay (tRCD)

Cada chip de memória é organizado internamente como uma matriz. Na interseção de cada linha e coluna temos um pequeno capacitor responsável por armazenar um “0” ou “1” – o dado. Internamente, o processo de acessar um dado armazenado é feito ativando-se a linha onde ele está localizado e, em seguida, a coluna. Esta ativação é feita por dois sinais de controle chamados RAS (Row Address Strobe) e CAS (Column Address Strobe). Quanto menor for o tempo entre esses dois sinais, melhor, já que o dado será lido mais rapidamente. O parâmetro RAS to CAS Delay ou (tRCD) mede este tempo. Na Figura 5 ilustramos isto, mostrando uma memória com tRCD=3.

Figura 5: RAS to CAS Delay (tRCD)

Como você pode ver, o parâmetro RAS to CAS Delay é também o número de pulsos de clock entre o comando “Active” (“ativar”) e um comando “Read” (“leitura”) ou “Write” (“escrita”).

Assim como acontece com a latência do CAS, o parâmetro RAS to CAS Delay funciona com o clock real da memória (que é metade do clock rotulado), e quanto menor for este parâmetro, mais rápido a memória será, já que ela começará ler ou escrever dados mais rapidamente.

-

5

5

-

1

1

Respostas recomendadas

Crie uma conta ou entre para comentar

Você precisa ser um usuário para fazer um comentário

Criar uma conta

Crie uma nova conta em nossa comunidade. É fácil!

Crie uma nova contaEntrar

Já tem uma conta? Faça o login.

Entrar agora