Conjuntos de Instruções

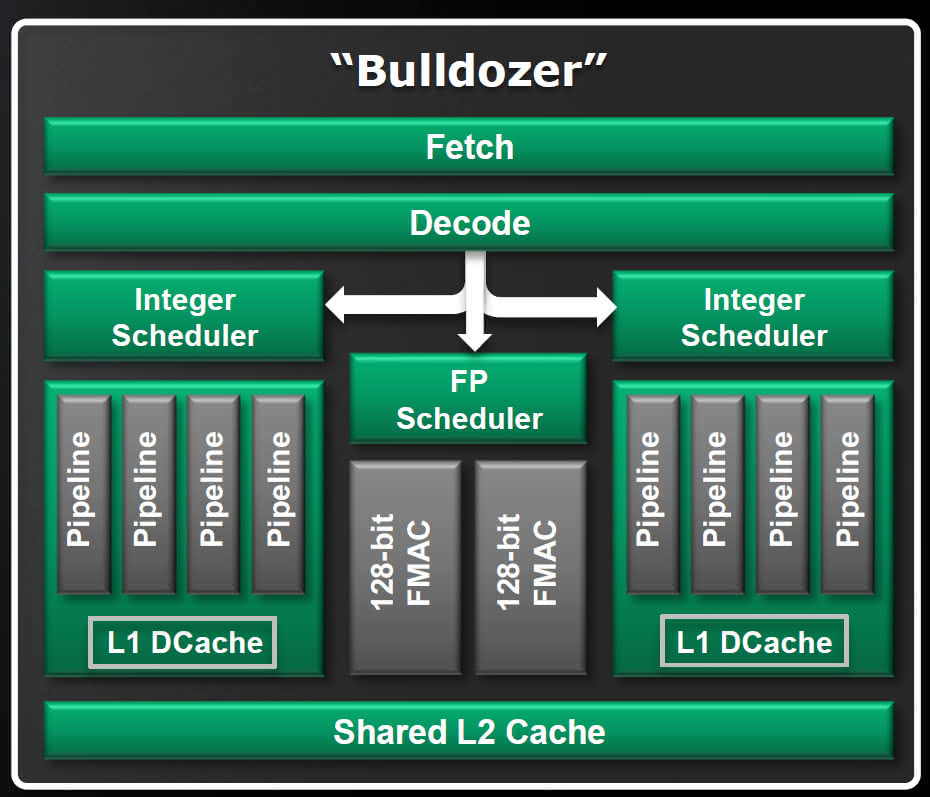

A arquitetura Bulldozer, além de ser compatível com as instruções x86, suportará os seguintes conjuntos de instruções adicionais:

- SSE4.1 e SSE4.2

- AVX (Advanced Vector Extensions ou Extensões de Vetor Avançadas) com dois subconjuntos adicionais, chamados XOP e FMA4

- AES (Advanced Encryption Standard ou Padrão de Criptografia Avançada)

- LWP (Light Weight Profiling ou Perfil “Peso Leve”)

Mas o que isso significa afinal? Vejamos.

SSE4.1 e SSE4.2

Finalmente os processadores da AMD terão suporte às instruções SSE4. Atualmente os processadores da AMD não suportam esses conjuntos de instruções, que aumentam o desempenho de aplicações multimídia (imagem e processamento de vídeo) que fazem uso dessas instruções. Os atuais processadores da AMD suportam um conjunto de instruções proprietário chamado SSE4a, que não é a mesma coisa de SSE4.

AVX (Advanced Vector Extensions ou Extensões de Vetor Avançadas)

Há algum tempo, a AMD propôs o conjunto de instruções SSE5. Como a Intel decidiu criar sua própria implementação do que seriam as instruções SSE5, chamada AVX (Advanced Vector Extensions ou Extensões de Vetor Avançadas), a AMD incluiu este conjunto de instruções na arquitetura Bulldozer.

As instruções AVX também serão suportadas pelos novos processadores da Intel baseados em sua arquitetura Sandy Bridge, e utilizarão o mesmo conceito SIMD (Single Instruction, Multiple Data ou Instrução Simples, Múltiplos Dados) introduzido com as instruções MMX e usado pelas instruções SSE (Streaming SIMD Extensions ou Extensões de Fluxo SIMD). Este conceito consiste em usar um único registrador grande para armazenar vários dados menores e então processá-los de uma só vez, aumentado o desempenho.

O conjunto de instruções AVX traz 12 novas instruções e aumenta o tamanho dos registradores XMM de 128 bits para 256 bits.

Na arquitetura Bulldozer, a AMD decidiu incluir algumas das instruções originalmente propostas para o conjunto de instruções SSE5. Portanto, a implementação AVX da arquitetura Bulldozer é mais completa do que a da Intel. Essas instruções adicionais são chamadas XOP e FMA4, e uma descrição detalhada sobre elas pode ser encontrada aqui. Nas apresentações do Bulldozer a AMD anuncia o conjunto de instruções AVX como “também” tendo o subconjunto FMAC (Fused Multiply-Accumulate, Multiplicação-Acumulação Fundido), mas este subconjunto de instruções é na verdade parte das instruções XOP. O “AMD 4-operand form” (“formato de quatro operandos da AMD”) anunciado nas apresentações da AMD é simplesmente o novo formado usado pelas instruções XOP e sua menção também é completamente redundante.

AES (Advanced Encryption Standard ou Padrão de Criptografia Avançada)

Este conjunto de instruções já está sendo usado nos novos processadores Intel baseados na arquitetura “Westmere” e modelos futuros (exceto Core i3), e consiste de seis novas instruções para tratar especificamente com criptografia. A Intel chama este conjunto de instruções de AES-NI. Uma descrição detalhada dessas instruções pode ser encontrada aqui.

LWP (Light Weight Profiling ou Perfil Peso Leve)

As instruções LWP permitem monitorar o desempenho de programas, e pode ser usado por desenvolvedores para ajustarem seus programas a obterem o maior desempenho possível, por exemplo. Este conjunto de instruções adicional tem seis novas instruções e uma descrição detalhada sobre ele pode ser encontrada aqui.

Respostas recomendadas

Crie uma conta ou entre para comentar

Você precisa ser um usuário para fazer um comentário

Criar uma conta

Crie uma nova conta em nossa comunidade. É fácil!

Crie uma nova contaEntrar

Já tem uma conta? Faça o login.

Entrar agora